rtl Architecture Reference

Inheritance diagram for rtl:

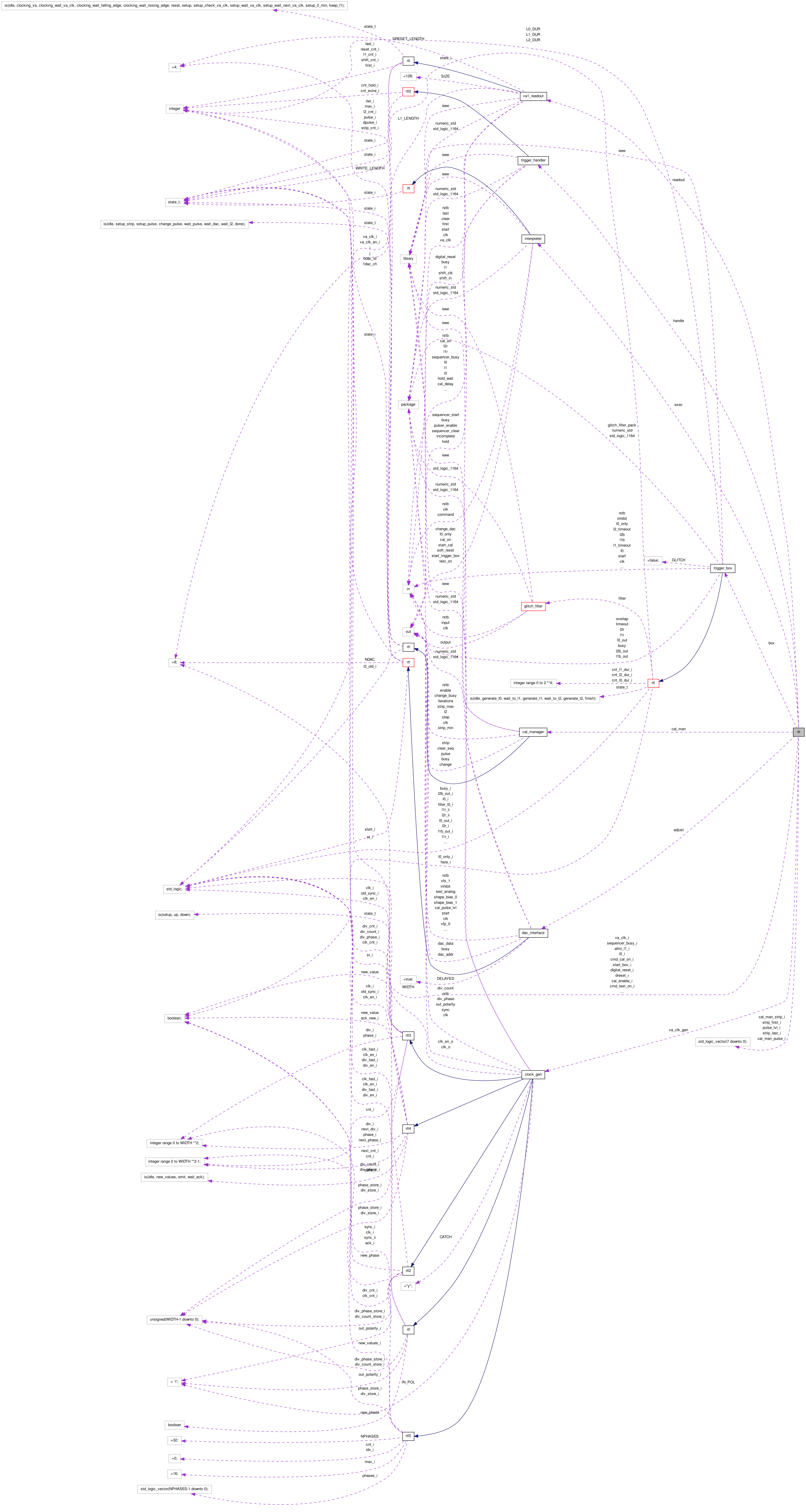

Collaboration diagram for rtl:

Signals | |

| l0_only_i | std_logic |

| start_box_i | std_logic |

| cmd_cal_on_i | std_logic |

| cmd_test_on_i | std_logic |

| cmd_change_dac_i | std_logic |

| soft_reset_i | std_logic |

| l0_i | std_logic |

| l1b_i | std_logic |

| l2b_i | std_logic |

| trg_clear_seq_i | std_logic |

| box_busy_i | std_logic |

| handler_busy_i | std_logic |

| sequencer_busy_i | std_logic |

| dac_busy_i | std_logic |

| l2r_i | std_logic |

| l1r_i | std_logic |

| incomplete_i | std_logic |

| overlap_i | std_logic |

| timeout_i | std_logic |

| va_clk_i | std_logic |

| sequencer_start_i | std_logic |

| sequencer_clear_i | std_logic |

| cal_man_start_i | std_logic |

| cal_man_busy_i | std_logic |

| cal_man_change_i | std_logic |

| cal_man_strip_i | std_logic_vector ( 7 downto 0 ) |

| cal_man_pulse_i | std_logic_vector ( 7 downto 0 ) |

| cal_clear_seq_i | std_logic |

| strip_first_i | std_logic_vector ( 7 downto 0 ) |

| strip_last_i | std_logic_vector ( 7 downto 0 ) |

| pulse_lvl_i | std_logic_vector ( 7 downto 0 ) |

| dac_start_i | std_logic |

| test_on_i | std_logic |

| cal_on_i | std_logic |

| dreset_i | std_logic |

| altro_l1_i | std_logic |

| hold_i | std_logic |

| shift_clk_i | std_logic |

| shift_in_i | std_logic |

| sample_clk_i | std_logic |

| digital_reset_i | std_logic |

| cal_enable_i | std_logic |

Component Instantiations | |

| exec | interpreter <Entity interpreter> |

| cal_man | cal_manager <Entity cal_manager> |

| box | trigger_box <Entity trigger_box> |

| handle | trigger_handler <Entity trigger_handler> |

| readout | va1_readout <Entity va1_readout> |

| adjust | dac_interface <Entity dac_interface> |

| va_clk_gen | clock_gen <Entity clock_gen> |

Member Data Documentation

adjust dac_interface [Component Instantiation] |

altro_l1_i std_logic [Signal] |

box trigger_box [Component Instantiation] |

box_busy_i std_logic [Signal] |

cal_clear_seq_i std_logic [Signal] |

cal_enable_i std_logic [Signal] |

cal_man cal_manager [Component Instantiation] |

cal_man_busy_i std_logic [Signal] |

cal_man_change_i std_logic [Signal] |

cal_man_pulse_i std_logic_vector ( 7 downto 0 ) [Signal] |

cal_man_start_i std_logic [Signal] |

cal_man_strip_i std_logic_vector ( 7 downto 0 ) [Signal] |

cal_on_i std_logic [Signal] |

cmd_cal_on_i std_logic [Signal] |

cmd_change_dac_i std_logic [Signal] |

cmd_test_on_i std_logic [Signal] |

dac_busy_i std_logic [Signal] |

dac_start_i std_logic [Signal] |

digital_reset_i std_logic [Signal] |

dreset_i std_logic [Signal] |

exec interpreter [Component Instantiation] |

handle trigger_handler [Component Instantiation] |

handler_busy_i std_logic [Signal] |

hold_i std_logic [Signal] |

incomplete_i std_logic [Signal] |

l0_i std_logic [Signal] |

l0_only_i std_logic [Signal] |

l1b_i std_logic [Signal] |

l1r_i std_logic [Signal] |

l2b_i std_logic [Signal] |

l2r_i std_logic [Signal] |

overlap_i std_logic [Signal] |

pulse_lvl_i std_logic_vector ( 7 downto 0 ) [Signal] |

readout va1_readout [Component Instantiation] |

sample_clk_i std_logic [Signal] |

sequencer_busy_i std_logic [Signal] |

sequencer_clear_i std_logic [Signal] |

sequencer_start_i std_logic [Signal] |

shift_clk_i std_logic [Signal] |

shift_in_i std_logic [Signal] |

soft_reset_i std_logic [Signal] |

start_box_i std_logic [Signal] |

strip_first_i std_logic_vector ( 7 downto 0 ) [Signal] |

strip_last_i std_logic_vector ( 7 downto 0 ) [Signal] |

test_on_i std_logic [Signal] |

timeout_i std_logic [Signal] |

trg_clear_seq_i std_logic [Signal] |

va_clk_gen clock_gen [Component Instantiation] |

va_clk_i std_logic [Signal] |

The documentation for this class was generated from the following file:

- bc/fmdd/fmdd.vhd

1.6.2-20100208

1.6.2-20100208