rtl Architecture Reference

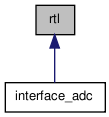

Inheritance diagram for rtl:

Collaboration diagram for rtl:

Signals | |

| address_rom_i | std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) |

| data_rom_i | std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) |

| data_valid_i | std_logic |

| en_add_i | std_logic |

| error_i | std_logic |

| ready_i | std_logic |

| s_i | std_logic |

| width_i | std_logic |

| data_seq_i | std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) |

| new_data_i | std_logic |

| rw_i | std_logic |

| start_i | std_logic |

| stop_i | std_logic |

Component Instantiations | |

| instructions_rom | rom <Entity rom> |

| seq | sequencer <Entity sequencer> |

| i2c_master | master <Entity master> |

Member Data Documentation

address_rom_i std_logic_vector ( 9 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

data_rom_i std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

data_seq_i std_logic_vector ( 7 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

data_valid_i std_logic [Signal] |

en_add_i std_logic [Signal] |

error_i std_logic [Signal] |

i2c_master master [Component Instantiation] |

instructions_rom rom [Component Instantiation] |

new_data_i std_logic [Signal] |

ready_i std_logic [Signal] |

rw_i std_logic [Signal] |

s_i std_logic [Signal] |

start_i std_logic [Signal] |

stop_i std_logic [Signal] |

width_i std_logic [Signal] |

The documentation for this class was generated from the following file:

- bc/bc_core/interface_adc/interface_adc.vhd

1.6.2-20100208

1.6.2-20100208