flex10ke_ram_slice Entity Reference

Inheritance diagram for flex10ke_ram_slice:

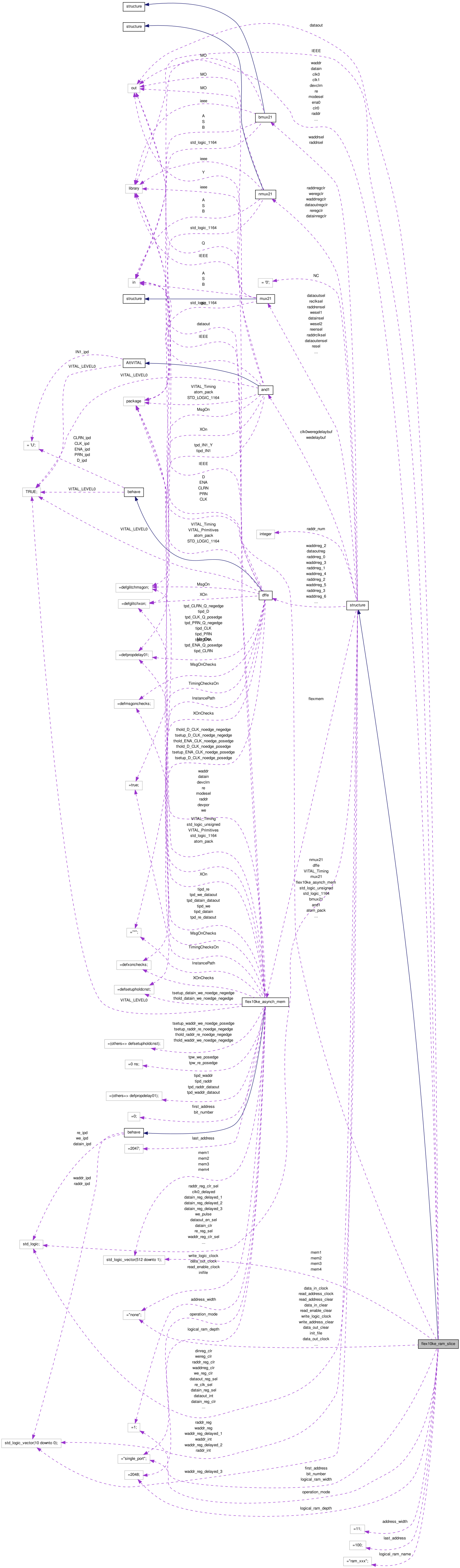

Collaboration diagram for flex10ke_ram_slice:

Architectures | |

| structure | Architecture |

Libraries | |

| IEEE | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

| VITAL_Timing | |

| atom_pack | Package <atom_pack> |

Generics | |

| operation_mode | string := " single_port " |

| logical_ram_name | string := " ram_xxx " |

| logical_ram_depth | integer := 2048 |

| logical_ram_width | integer := 1 |

| address_width | integer := 11 |

| data_in_clock | string := " none " |

| data_in_clear | string := " none " |

| write_logic_clock | string := " none " |

| write_address_clear | string := " none " |

| write_enable_clear | string := " none " |

| read_enable_clock | string := " none " |

| read_enable_clear | string := " none " |

| read_address_clock | string := " none " |

| read_address_clear | string := " none " |

| data_out_clock | string := " none " |

| data_out_clear | string := " none " |

| init_file | string := " none " |

| first_address | integer := 1 |

| last_address | integer := 100 |

| bit_number | integer := 1 |

| mem1 | std_logic_vector ( 512 downto 1 ) |

| mem2 | std_logic_vector ( 512 downto 1 ) |

| mem3 | std_logic_vector ( 512 downto 1 ) |

| mem4 | std_logic_vector ( 512 downto 1 ) |

Ports | |

| datain | in std_logic |

| clr0 | in std_logic |

| clk0 | in std_logic |

| clk1 | in std_logic |

| ena0 | in std_logic |

| ena1 | in std_logic |

| we | in std_logic |

| re | in std_logic |

| waddr | in std_logic_vector ( 10 downto 0 ) |

| raddr | in std_logic_vector ( 10 downto 0 ) |

| devclrn | in std_logic := ' 1 ' |

| devpor | in std_logic := ' 1 ' |

| modesel | in std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| dataout | out std_logic |

Member Data Documentation

address_width integer := 11 [Generic] |

atom_pack package [Package] |

bit_number integer := 1 [Generic] |

clk0 in std_logic [Port] |

clk1 in std_logic [Port] |

clr0 in std_logic [Port] |

data_in_clear string := " none " [Generic] |

data_in_clock string := " none " [Generic] |

data_out_clear string := " none " [Generic] |

data_out_clock string := " none " [Generic] |

datain in std_logic [Port] |

dataout out std_logic [Port] |

devclrn in std_logic := ' 1 ' [Port] |

devpor in std_logic := ' 1 ' [Port] |

ena0 in std_logic [Port] |

ena1 in std_logic [Port] |

first_address integer := 1 [Generic] |

flex10ke_asynch_mem package [Package] |

Reimplemented from structure.

IEEE library [Library] |

init_file string := " none " [Generic] |

last_address integer := 100 [Generic] |

logical_ram_depth integer := 2048 [Generic] |

logical_ram_name string := " ram_xxx " [Generic] |

logical_ram_width integer := 1 [Generic] |

mem1 std_logic_vector ( 512 downto 1 ) [Generic] |

mem2 std_logic_vector ( 512 downto 1 ) [Generic] |

mem3 std_logic_vector ( 512 downto 1 ) [Generic] |

mem4 std_logic_vector ( 512 downto 1 ) [Generic] |

modesel in std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) [Port] |

operation_mode string := " single_port " [Generic] |

raddr in std_logic_vector ( 10 downto 0 ) [Port] |

re in std_logic [Port] |

read_address_clear string := " none " [Generic] |

read_address_clock string := " none " [Generic] |

read_enable_clear string := " none " [Generic] |

read_enable_clock string := " none " [Generic] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

VITAL_Timing package [Package] |

waddr in std_logic_vector ( 10 downto 0 ) [Port] |

we in std_logic [Port] |

write_address_clear string := " none " [Generic] |

write_enable_clear string := " none " [Generic] |

write_logic_clock string := " none " [Generic] |

The documentation for this class was generated from the following file:

- flex10ke/flex10ke_atoms.vhd

1.6.2-20100208

1.6.2-20100208