structure Architecture Reference

Inheritance diagram for structure:

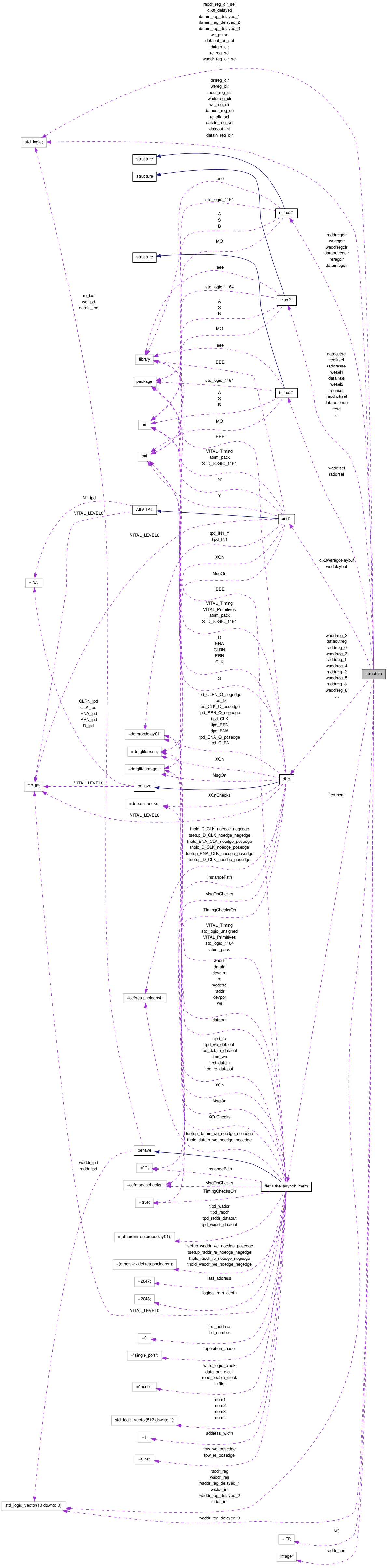

Collaboration diagram for structure:

Member Data Documentation

and1 [Component] |

Reimplemented in flex10ke_ram_slice.

bmux21 [Component] |

Reimplemented in flex10ke_ram_slice.

clk0_delayed std_logic [Signal] |

clk0weregdelaybuf and1 [Component Instantiation] |

datain_clr std_logic [Signal] |

datain_int std_logic [Signal] |

datain_reg std_logic [Signal] |

datain_reg_clr std_logic [Signal] |

datain_reg_clr_sel std_logic [Signal] |

datain_reg_delayed_1 std_logic [Signal] |

datain_reg_delayed_2 std_logic [Signal] |

datain_reg_delayed_3 std_logic [Signal] |

datain_reg_sel std_logic [Signal] |

datainregclr nmux21 [Component Instantiation] |

dataout_en_sel std_logic [Signal] |

dataout_int std_logic [Signal] |

dataout_reg std_logic [Signal] |

dataout_reg_clr std_logic [Signal] |

dataout_reg_clr_sel std_logic [Signal] |

dataout_reg_sel std_logic [Signal] |

dataout_tmp std_logic [Signal] |

dataouten std_logic [Signal] |

dataoutensel mux21 [Component Instantiation] |

dataoutreg dffe [Component Instantiation] |

dataoutreg_clr std_logic [Signal] |

dataoutregclr nmux21 [Component Instantiation] |

dataoutsel mux21 [Component Instantiation] |

dffe [Component] |

Reimplemented in flex10ke_ram_slice.

dinreg_clr std_logic [Signal] |

flex10ke_asynch_mem [Component] |

Reimplemented in flex10ke_ram_slice.

flexmem flex10ke_asynch_mem [Component Instantiation] |

mux21 [Component] |

Reimplemented in flex10ke_ram_slice.

NC std_logic := ' 0 ' [Signal] |

nmux21 [Component] |

Reimplemented in flex10ke_ram_slice.

raddr_clk std_logic [Signal] |

raddr_clk_sel std_logic [Signal] |

raddr_en_sel std_logic [Signal] |

raddr_int std_logic_vector ( 10 downto 0 ) [Signal] |

raddr_num integer [Signal] |

raddr_reg std_logic_vector ( 10 downto 0 ) [Signal] |

raddr_reg_clr std_logic [Signal] |

raddr_reg_clr_sel std_logic [Signal] |

raddr_reg_sel std_logic [Signal] |

raddrclksel mux21 [Component Instantiation] |

raddren std_logic [Signal] |

raddrensel mux21 [Component Instantiation] |

raddrreg_0 dffe [Component Instantiation] |

raddrreg_1 dffe [Component Instantiation] |

raddrreg_10 dffe [Component Instantiation] |

raddrreg_2 dffe [Component Instantiation] |

raddrreg_3 dffe [Component Instantiation] |

raddrreg_4 dffe [Component Instantiation] |

raddrreg_5 dffe [Component Instantiation] |

raddrreg_6 dffe [Component Instantiation] |

raddrreg_7 dffe [Component Instantiation] |

raddrreg_8 dffe [Component Instantiation] |

raddrreg_9 dffe [Component Instantiation] |

raddrreg_clr std_logic [Signal] |

raddrregclr nmux21 [Component Instantiation] |

re_clk std_logic [Signal] |

re_clk_sel std_logic [Signal] |

re_en_sel std_logic [Signal] |

re_int std_logic [Signal] |

re_reg std_logic [Signal] |

re_reg_clr std_logic [Signal] |

re_reg_clr_sel std_logic [Signal] |

re_reg_sel std_logic [Signal] |

reen std_logic [Signal] |

rereg_clr std_logic [Signal] |

valid_addr std_logic [Signal] |

waddr_int std_logic_vector ( 10 downto 0 ) [Signal] |

waddr_reg std_logic_vector ( 10 downto 0 ) [Signal] |

waddr_reg_clr std_logic [Signal] |

waddr_reg_clr_sel std_logic [Signal] |

waddr_reg_delayed_1 std_logic_vector ( 10 downto 0 ) [Signal] |

waddr_reg_delayed_2 std_logic_vector ( 10 downto 0 ) [Signal] |

waddr_reg_delayed_3 std_logic_vector ( 10 downto 0 ) [Signal] |

waddrreg_0 dffe [Component Instantiation] |

waddrreg_1 dffe [Component Instantiation] |

waddrreg_10 dffe [Component Instantiation] |

waddrreg_2 dffe [Component Instantiation] |

waddrreg_3 dffe [Component Instantiation] |

waddrreg_4 dffe [Component Instantiation] |

waddrreg_5 dffe [Component Instantiation] |

waddrreg_6 dffe [Component Instantiation] |

waddrreg_7 dffe [Component Instantiation] |

waddrreg_8 dffe [Component Instantiation] |

waddrreg_9 dffe [Component Instantiation] |

waddrreg_clr std_logic [Signal] |

waddrregclr nmux21 [Component Instantiation] |

we_int std_logic [Signal] |

we_pulse std_logic [Signal] |

we_reg std_logic [Signal] |

we_reg_clr std_logic [Signal] |

we_reg_clr_sel std_logic [Signal] |

we_reg_mux std_logic [Signal] |

we_reg_mux_delayed std_logic [Signal] |

wedelaybuf and1 [Component Instantiation] |

wereg_clr std_logic [Signal] |

write_reg_sel std_logic [Signal] |

The documentation for this class was generated from the following file:

- flex10ke/flex10ke_atoms.vhd

1.6.2-20100208

1.6.2-20100208