flex10ke_asynch_mem Entity Reference

Inheritance diagram for flex10ke_asynch_mem:

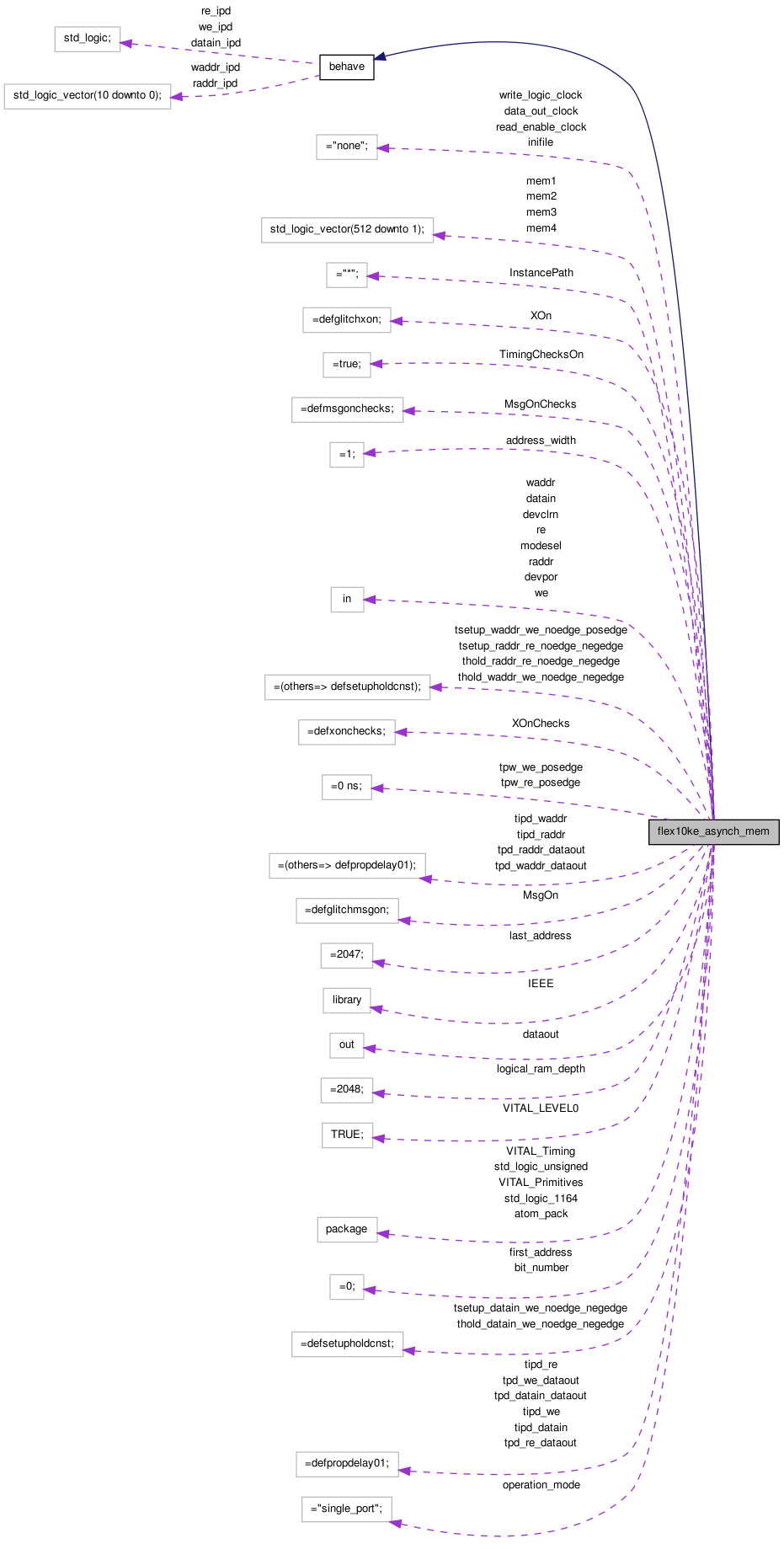

Collaboration diagram for flex10ke_asynch_mem:

Architectures | |

| behave | Architecture |

Libraries | |

| IEEE | |

Packages | |

| std_logic_1164 | |

| std_logic_unsigned | |

| VITAL_Timing | |

| VITAL_Primitives | |

| atom_pack | Package <atom_pack> |

Generics | |

| logical_ram_depth | integer := 2048 |

| inifile | string := " none " |

| address_width | integer := 1 |

| first_address | integer := 0 |

| last_address | integer := 2047 |

| mem1 | std_logic_vector ( 512 downto 1 ) |

| mem2 | std_logic_vector ( 512 downto 1 ) |

| mem3 | std_logic_vector ( 512 downto 1 ) |

| mem4 | std_logic_vector ( 512 downto 1 ) |

| bit_number | integer := 0 |

| write_logic_clock | string := " none " |

| read_enable_clock | string := " none " |

| data_out_clock | string := " none " |

| operation_mode | string := " single_port " |

| TimingChecksOn | boolean := true |

| MsgOn | boolean := DefGlitchMsgOn |

| XOn | boolean := DefGlitchXOn |

| MsgOnChecks | boolean := DefMsgOnChecks |

| XOnChecks | boolean := DefXOnChecks |

| InstancePath | string := " * " |

| tsetup_waddr_we_noedge_posedge | vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) |

| thold_waddr_we_noedge_negedge | vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) |

| tsetup_datain_we_noedge_negedge | vitaldelaytype := DefSetupHoldCnst |

| thold_datain_we_noedge_negedge | vitaldelaytype := DefSetupHoldCnst |

| tsetup_raddr_re_noedge_negedge | vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) |

| thold_raddr_re_noedge_negedge | vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) |

| tpd_raddr_dataout | vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) |

| tpd_waddr_dataout | vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) |

| tpd_re_dataout | vitaldelaytype01 := DefPropDelay01 |

| tpd_datain_dataout | vitaldelaytype01 := DefPropDelay01 |

| tpd_we_dataout | vitaldelaytype01 := DefPropDelay01 |

| tipd_datain | vitaldelaytype01 := DefPropDelay01 |

| tipd_we | vitaldelaytype01 := DefPropDelay01 |

| tipd_re | vitaldelaytype01 := DefPropDelay01 |

| tipd_raddr | vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) |

| tipd_waddr | vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) |

| tpw_we_posedge | vitaldelaytype := 0 ns |

| tpw_re_posedge | vitaldelaytype := 0 ns |

Ports | |

| datain | in std_logic := ' 0 ' |

| we | in std_logic := ' 0 ' |

| re | in std_logic := ' 1 ' |

| raddr | in std_logic_vector ( 10 downto 0 ) := " 00000000000 " |

| waddr | in std_logic_vector ( 10 downto 0 ) := " 00000000000 " |

| devclrn | in std_logic := ' 1 ' |

| devpor | in std_logic := ' 1 ' |

| modesel | in std_logic_vector ( 15 downto 0 ) := " 0000000000000000 " |

| dataout | out std_logic |

Attributes | |

| VITAL_LEVEL0 | TRUE |

Member Data Documentation

address_width integer := 1 [Generic] |

atom_pack package [Package] |

bit_number integer := 0 [Generic] |

data_out_clock string := " none " [Generic] |

datain in std_logic := ' 0 ' [Port] |

dataout out std_logic [Port] |

devclrn in std_logic := ' 1 ' [Port] |

devpor in std_logic := ' 1 ' [Port] |

first_address integer := 0 [Generic] |

IEEE library [Library] |

inifile string := " none " [Generic] |

InstancePath string := " * " [Generic] |

last_address integer := 2047 [Generic] |

logical_ram_depth integer := 2048 [Generic] |

mem1 std_logic_vector ( 512 downto 1 ) [Generic] |

mem2 std_logic_vector ( 512 downto 1 ) [Generic] |

mem3 std_logic_vector ( 512 downto 1 ) [Generic] |

mem4 std_logic_vector ( 512 downto 1 ) [Generic] |

modesel in std_logic_vector ( 15 downto 0 ) := " 0000000000000000 " [Port] |

MsgOn boolean := DefGlitchMsgOn [Generic] |

MsgOnChecks boolean := DefMsgOnChecks [Generic] |

operation_mode string := " single_port " [Generic] |

raddr in std_logic_vector ( 10 downto 0 ) := " 00000000000 " [Port] |

re in std_logic := ' 1 ' [Port] |

read_enable_clock string := " none " [Generic] |

std_logic_1164 package [Package] |

std_logic_unsigned package [Package] |

thold_datain_we_noedge_negedge vitaldelaytype := DefSetupHoldCnst [Generic] |

thold_raddr_re_noedge_negedge vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) [Generic] |

thold_waddr_we_noedge_negedge vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) [Generic] |

TimingChecksOn boolean := true [Generic] |

tipd_datain vitaldelaytype01 := DefPropDelay01 [Generic] |

tipd_raddr vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) [Generic] |

tipd_re vitaldelaytype01 := DefPropDelay01 [Generic] |

tipd_waddr vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) [Generic] |

tipd_we vitaldelaytype01 := DefPropDelay01 [Generic] |

tpd_datain_dataout vitaldelaytype01 := DefPropDelay01 [Generic] |

tpd_raddr_dataout vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) [Generic] |

tpd_re_dataout vitaldelaytype01 := DefPropDelay01 [Generic] |

tpd_waddr_dataout vitaldelayarraytype01 ( 10 downto 0 ) := ( others = > DefPropDelay01 ) [Generic] |

tpd_we_dataout vitaldelaytype01 := DefPropDelay01 [Generic] |

tpw_re_posedge vitaldelaytype := 0 ns [Generic] |

tpw_we_posedge vitaldelaytype := 0 ns [Generic] |

tsetup_datain_we_noedge_negedge vitaldelaytype := DefSetupHoldCnst [Generic] |

tsetup_raddr_re_noedge_negedge vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) [Generic] |

tsetup_waddr_we_noedge_posedge vitaldelayarraytype ( 10 downto 0 ) := ( others = > DefSetupHoldCnst ) [Generic] |

VITAL_LEVEL0 TRUE [Attribute] |

VITAL_Primitives package [Package] |

VITAL_Timing package [Package] |

waddr in std_logic_vector ( 10 downto 0 ) := " 00000000000 " [Port] |

we in std_logic := ' 0 ' [Port] |

write_logic_clock string := " none " [Generic] |

XOn boolean := DefGlitchXOn [Generic] |

XOnChecks boolean := DefXOnChecks [Generic] |

The documentation for this class was generated from the following file:

- flex10ke/flex10ke_atoms.vhd

1.6.2-20100208

1.6.2-20100208