rtl Architecture Reference

Inheritance diagram for rtl:

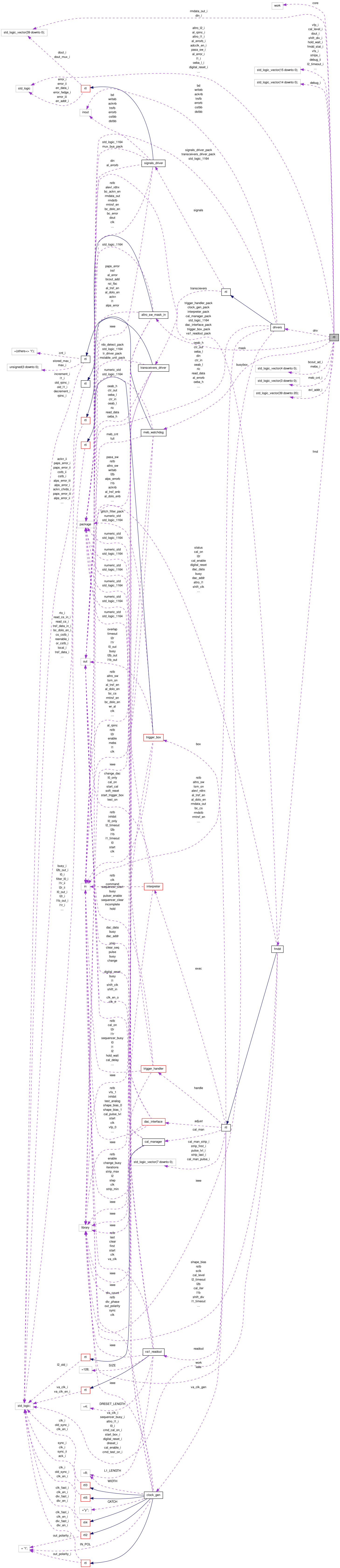

Collaboration diagram for rtl:

Signals | |

| cstb_i | std_logic |

| write_i | std_logic |

| dstb_i | std_logic |

| trsf_i | std_logic |

| l1_i | std_logic |

| l2_i | std_logic |

| ackn_i | std_logic |

| bc_dolo_en_i | std_logic |

| bc_cs_i | std_logic |

| al_cs_i | std_logic |

| wr_al_i | std_logic |

| bc_ackn_en_i | std_logic |

| bc_ackn_i | std_logic |

| bc_int_i | std_logic |

| bc_error_i | std_logic |

| din_i | std_logic_vector ( 39 downto 0 ) |

| sda_out_i | std_logic |

| slctr_i | std_logic |

| dout_i | std_logic_vector ( 15 downto 0 ) |

| paps_error_i | std_logic |

| alps_error_i | std_logic |

| rmtrsf_en_i | std_logic |

| rmtrsf_i | std_logic |

| rmdstb_i | std_logic |

| rmdata_out_i | std_logic_vector ( 39 downto 0 ) |

| adcclk_en_i | std_logic |

| tsm_on_i | std_logic |

| card_isolation_i | std_logic |

| evl_cstb_i | std_logic |

| alevl_rdtrx_i | std_logic |

| bc_master_i | std_logic |

| evl_addr_i | std_logic_vector ( 39 downto 20 ) |

| al_error_i | std_logic |

| al_errorb_i | std_logic |

| al_dolo_en_i | std_logic |

| al_trsf_en_i | std_logic |

| ackn_chrdo_i | std_logic |

| altro_sw_i | std_logic |

| pasa_sw_i | std_logic |

| al_rst_i | std_logic |

| or_rst_i | std_logic |

| hold_wait_i | std_logic_vector ( 15 downto 0 ) |

| l1_timeout_i | std_logic_vector ( 15 downto 0 ) |

| l2_timeout_i | std_logic_vector ( 15 downto 0 ) |

| shift_div_i | std_logic_vector ( 15 downto 0 ) |

| strips_i | std_logic_vector ( 15 downto 0 ) |

| cal_level_i | std_logic_vector ( 15 downto 0 ) |

| shape_bias_i | std_logic_vector ( 15 downto 0 ) |

| vfs_i | std_logic_vector ( 15 downto 0 ) |

| vfp_i | std_logic_vector ( 15 downto 0 ) |

| sample_div_i | std_logic_vector ( 15 downto 0 ) |

| fmdd_cmd_i | std_logic_vector ( 15 downto 0 ) |

| fmdd_stat_i | std_logic_vector ( 15 downto 0 ) |

| cal_iter_i | std_logic_vector ( 15 downto 0 ) |

| cal_delay_i | std_logic_vector ( 15 downto 0 ) |

| hold_i | std_logic |

| shift_clk_i | std_logic |

| shift_in_i | std_logic |

| sample_clk_i | std_logic |

| digital_reset_i | std_logic |

| bcout_ad_i | std_logic_vector ( 4 downto 0 ) |

| altro_l1_i | std_logic |

| altro_l2_i | std_logic |

| al_rpinc_i | std_logic |

| mebs_i | std_logic_vector ( 4 downto 0 ) |

| meb_cnt_i | std_logic_vector ( 3 downto 0 ) |

| meb_full_i | std_logic |

| test_d | std_logic |

| test_e | std_logic |

| test_f | std_logic |

| test_g | std_logic |

| test_h | std_logic |

| debug_i | std_logic_vector ( 14 downto 0 ) |

| debug_ii | std_logic_vector ( 15 downto 0 ) |

| oeba_l_i | std_logic |

| oeab_l_i | std_logic |

| oeba_h_i | std_logic |

| oeab_h_i | std_logic |

| fmd_busy_i | std_logic |

| l2r_i | std_logic |

Component Instantiations | |

| core | work |

| fmd | fmdd <Entity fmdd> |

| busybox | meb_watchdog <Entity meb_watchdog> |

| mask | altro_sw_mask_in <Entity altro_sw_mask_in> |

| driv | drivers <Entity drivers> |

Member Data Documentation

ackn_chrdo_i std_logic [Signal] |

ackn_i std_logic [Signal] |

adcclk_en_i std_logic [Signal] |

al_cs_i std_logic [Signal] |

al_dolo_en_i std_logic [Signal] |

al_error_i std_logic [Signal] |

al_errorb_i std_logic [Signal] |

al_rpinc_i std_logic [Signal] |

al_rst_i std_logic [Signal] |

al_trsf_en_i std_logic [Signal] |

alevl_rdtrx_i std_logic [Signal] |

alps_error_i std_logic [Signal] |

altro_l1_i std_logic [Signal] |

altro_l2_i std_logic [Signal] |

altro_sw_i std_logic [Signal] |

bc_ackn_en_i std_logic [Signal] |

bc_ackn_i std_logic [Signal] |

bc_cs_i std_logic [Signal] |

bc_dolo_en_i std_logic [Signal] |

bc_error_i std_logic [Signal] |

bc_int_i std_logic [Signal] |

bc_master_i std_logic [Signal] |

bcout_ad_i std_logic_vector ( 4 downto 0 ) [Signal] |

busybox meb_watchdog [Component Instantiation] |

cal_delay_i std_logic_vector ( 15 downto 0 ) [Signal] |

cal_iter_i std_logic_vector ( 15 downto 0 ) [Signal] |

cal_level_i std_logic_vector ( 15 downto 0 ) [Signal] |

card_isolation_i std_logic [Signal] |

core work [Component Instantiation] |

cstb_i std_logic [Signal] |

debug_i std_logic_vector ( 14 downto 0 ) [Signal] |

debug_ii std_logic_vector ( 15 downto 0 ) [Signal] |

digital_reset_i std_logic [Signal] |

din_i std_logic_vector ( 39 downto 0 ) [Signal] |

dout_i std_logic_vector ( 15 downto 0 ) [Signal] |

dstb_i std_logic [Signal] |

evl_addr_i std_logic_vector ( 39 downto 20 ) [Signal] |

evl_cstb_i std_logic [Signal] |

fmd_busy_i std_logic [Signal] |

fmdd_cmd_i std_logic_vector ( 15 downto 0 ) [Signal] |

fmdd_stat_i std_logic_vector ( 15 downto 0 ) [Signal] |

hold_i std_logic [Signal] |

hold_wait_i std_logic_vector ( 15 downto 0 ) [Signal] |

l1_i std_logic [Signal] |

l1_timeout_i std_logic_vector ( 15 downto 0 ) [Signal] |

l2_i std_logic [Signal] |

l2_timeout_i std_logic_vector ( 15 downto 0 ) [Signal] |

l2r_i std_logic [Signal] |

mask altro_sw_mask_in [Component Instantiation] |

meb_cnt_i std_logic_vector ( 3 downto 0 ) [Signal] |

meb_full_i std_logic [Signal] |

mebs_i std_logic_vector ( 4 downto 0 ) [Signal] |

oeab_h_i std_logic [Signal] |

oeab_l_i std_logic [Signal] |

oeba_h_i std_logic [Signal] |

oeba_l_i std_logic [Signal] |

or_rst_i std_logic [Signal] |

paps_error_i std_logic [Signal] |

pasa_sw_i std_logic [Signal] |

rmdata_out_i std_logic_vector ( 39 downto 0 ) [Signal] |

rmdstb_i std_logic [Signal] |

rmtrsf_en_i std_logic [Signal] |

rmtrsf_i std_logic [Signal] |

sample_clk_i std_logic [Signal] |

sample_div_i std_logic_vector ( 15 downto 0 ) [Signal] |

sda_out_i std_logic [Signal] |

shape_bias_i std_logic_vector ( 15 downto 0 ) [Signal] |

shift_clk_i std_logic [Signal] |

shift_div_i std_logic_vector ( 15 downto 0 ) [Signal] |

shift_in_i std_logic [Signal] |

slctr_i std_logic [Signal] |

strips_i std_logic_vector ( 15 downto 0 ) [Signal] |

test_d std_logic [Signal] |

test_e std_logic [Signal] |

test_f std_logic [Signal] |

test_g std_logic [Signal] |

test_h std_logic [Signal] |

trsf_i std_logic [Signal] |

tsm_on_i std_logic [Signal] |

vfp_i std_logic_vector ( 15 downto 0 ) [Signal] |

vfs_i std_logic_vector ( 15 downto 0 ) [Signal] |

wr_al_i std_logic [Signal] |

write_i std_logic [Signal] |

The documentation for this class was generated from the following file:

- bc/bc.vhd

1.6.2-20100208

1.6.2-20100208