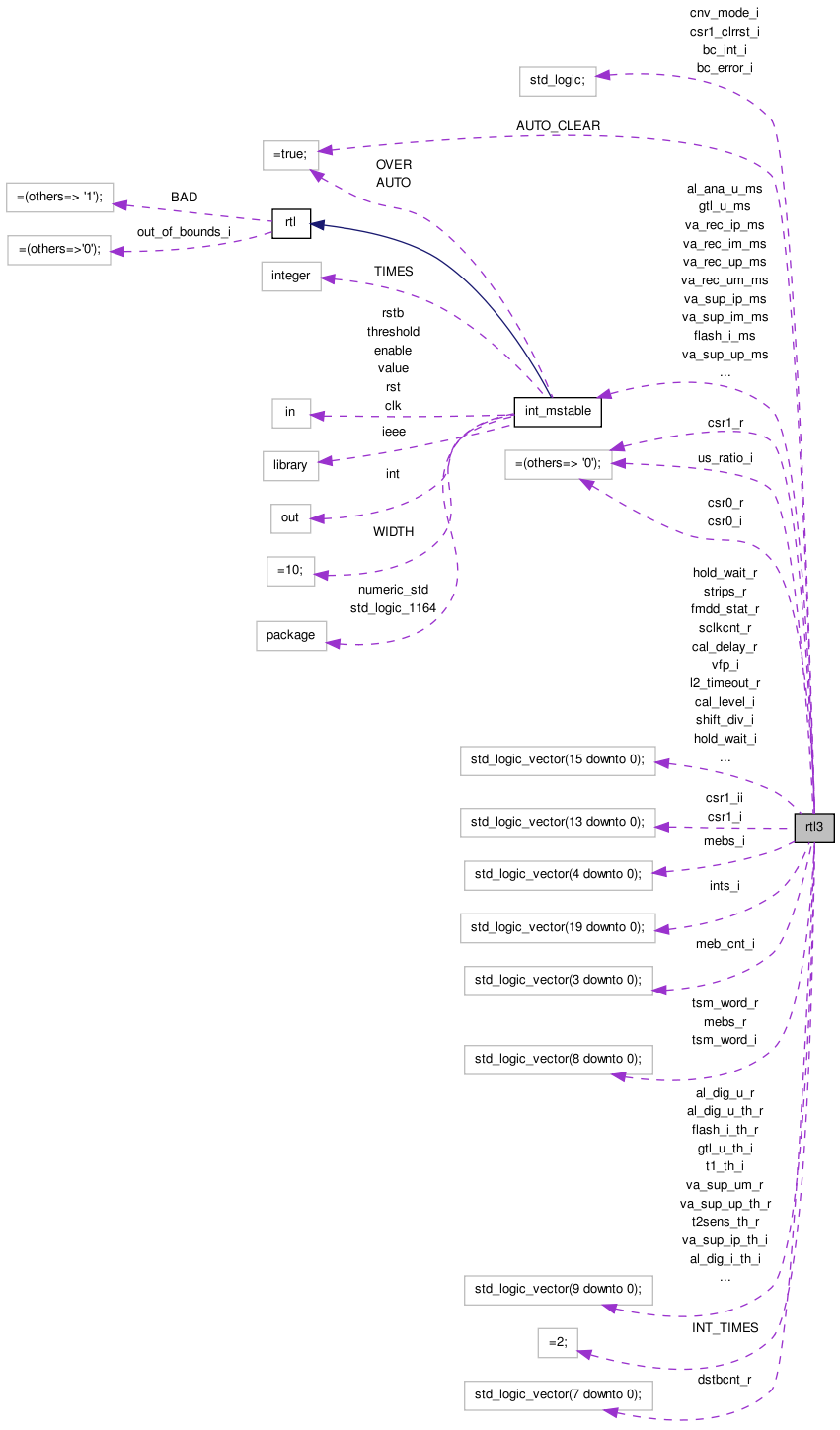

rtl3 Architecture Reference

Processes | |

| adc_register | ( clk , rstb ) |

| reg_register | ( clk , rstb ) |

| output_al | ( clk ) |

| output_sc | ( clk ) |

| ans_cmds | ( clk , rstb ) |

| errors | ( clk , rstb ) |

Constants | |

| INT_TIMES | integer := 2 |

| AUTO_CLEAR | boolean := true |

Signals | |

| t1_th_i | std_logic_vector ( 9 downto 0 ) |

| First ADC T. | |

| flash_i_th_i | std_logic_vector ( 9 downto 0 ) |

| I 3.3 V. | |

| al_dig_i_th_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro dig. | |

| al_ana_i_th_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro ana. | |

| va_rec_ip_th_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V VA. | |

| t1_i | std_logic_vector ( 9 downto 0 ) |

| First ADC T. | |

| flash_i_i | std_logic_vector ( 9 downto 0 ) |

| I 3.3 V. | |

| al_dig_i_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro dig. | |

| al_ana_i_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro ana. | |

| va_rec_ip_i | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V VA. | |

| t2_th_i | std_logic_vector ( 9 downto 0 ) |

| Second ADC T. | |

| va_sup_ip_th_i | std_logic_vector ( 9 downto 0 ) |

| I 1.5 V VA. | |

| va_rec_im_th_i | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V. | |

| va_sup_im_th_i | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V VA. | |

| gtl_u_th_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 V Digital. | |

| t2_i | std_logic_vector ( 9 downto 0 ) |

| Second ADC T. | |

| va_sup_ip_i | std_logic_vector ( 9 downto 0 ) |

| I 1.5 V VA. | |

| va_rec_im_i | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V. | |

| va_sup_im_i | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V VA. | |

| gtl_u_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 V Digital. | |

| t3_th_i | std_logic_vector ( 9 downto 0 ) |

| Third ADC T. | |

| t1sens_th_i | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 1. | |

| t2sens_th_i | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 2. | |

| al_dig_u_th_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro dig. | |

| al_ana_u_th_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro ana. | |

| t3_i | std_logic_vector ( 9 downto 0 ) |

| Third ADC T. | |

| t1sens_i | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 1. | |

| t2sens_i | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 2. | |

| al_dig_u_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro dig. | |

| al_ana_u_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro ana. | |

| t4_th_i | std_logic_vector ( 9 downto 0 ) |

| Forth ADC T. | |

| va_rec_up_th_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 VA (m). | |

| va_sup_up_th_i | std_logic_vector ( 9 downto 0 ) |

| U 1.5 VA (m). | |

| va_sup_um_th_i | std_logic_vector ( 9 downto 0 ) |

| U -2.0 VA (m). | |

| va_rec_um_th_i | std_logic_vector ( 9 downto 0 ) |

| U -2.0 (m). | |

| t4_i | std_logic_vector ( 9 downto 0 ) |

| Forth ADC T. | |

| va_rec_up_i | std_logic_vector ( 9 downto 0 ) |

| U 2.5 VA (m). | |

| va_sup_up_i | std_logic_vector ( 9 downto 0 ) |

| U 1.5 VA (m). | |

| va_sup_um_i | std_logic_vector ( 9 downto 0 ) |

| U -2.0 VA (m). | |

| va_rec_um_i | std_logic_vector ( 9 downto 0 ) |

| U -2.0 (m). | |

| l1cnt_i | std_logic_vector ( 15 downto 0 ) |

| L1 counter. | |

| l2cnt_i | std_logic_vector ( 15 downto 0 ) |

| L2 counter. | |

| sclkcnt_i | std_logic_vector ( 15 downto 0 ) |

| Slow clock counter. | |

| tsm_word_i | std_logic_vector ( 8 downto 0 ) |

| Test mode words. | |

| us_ratio_i | std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) |

| csr0_i | std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) |

| csr1_i | std_logic_vector ( 13 downto 0 ) |

| Config/Status 1. | |

| csr2_i | std_logic_vector ( 15 downto 0 ) |

| Config/Status 2. | |

| csr3_i | std_logic_vector ( 15 downto 0 ) |

| Config/Status 3. | |

| l0cnt_i | std_logic_vector ( 15 downto 0 ) |

| L0 counters. | |

| hold_wait_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Wait to hold. | |

| l1_timeout_i | std_logic_vector ( 15 downto 0 ) |

| FMD: L1 timeout. | |

| l2_timeout_i | std_logic_vector ( 15 downto 0 ) |

| FMD: L2 timeout. | |

| shift_div_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Shift clk. | |

| strips_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Strips. | |

| cal_level_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Cal pulse. | |

| cal_iter_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Cal events. | |

| shape_bias_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Shape bias. | |

| vfs_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Shape ref. | |

| vfp_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Preamp ref. | |

| sample_div_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Sample clk. | |

| fmdd_cmd_i | std_logic_vector ( 15 downto 0 ) |

| FMD: Commands. | |

| mebs_i | std_logic_vector ( 4 downto 0 ) |

| MEB config. | |

| cal_delay_i | std_logic_vector ( 15 downto 0 ) |

| CAL xtra delay. | |

| t1_th_r | std_logic_vector ( 9 downto 0 ) |

| First ADC T. | |

| flash_i_th_r | std_logic_vector ( 9 downto 0 ) |

| I 3.3 V. | |

| al_dig_i_th_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro dig. | |

| al_ana_i_th_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro ana. | |

| va_rec_ip_th_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V VA. | |

| t1_r | std_logic_vector ( 9 downto 0 ) |

| First ADC T. | |

| flash_i_r | std_logic_vector ( 9 downto 0 ) |

| I 3.3 V. | |

| al_dig_i_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro dig. | |

| al_ana_i_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V altro ana. | |

| va_rec_ip_r | std_logic_vector ( 9 downto 0 ) |

| I 2.5 V VA. | |

| t2_th_r | std_logic_vector ( 9 downto 0 ) |

| Second ADC T. | |

| va_sup_ip_th_r | std_logic_vector ( 9 downto 0 ) |

| I 1.5 V VA. | |

| va_rec_im_th_r | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V. | |

| va_sup_im_th_r | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V VA. | |

| gtl_u_th_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 V Digital. | |

| t2_r | std_logic_vector ( 9 downto 0 ) |

| Second ADC T. | |

| va_sup_ip_r | std_logic_vector ( 9 downto 0 ) |

| I 1.5 V VA. | |

| va_rec_im_r | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V. | |

| va_sup_im_r | std_logic_vector ( 9 downto 0 ) |

| I -2.0 V VA. | |

| gtl_u_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 V Digital. | |

| t3_th_r | std_logic_vector ( 9 downto 0 ) |

| Third ADC T. | |

| t1sens_th_r | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 1. | |

| t2sens_th_r | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 2. | |

| al_dig_u_th_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro dig. | |

| al_ana_u_th_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro analog. | |

| t3_r | std_logic_vector ( 9 downto 0 ) |

| Third ADC T. | |

| t1sens_r | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 1. | |

| t2sens_r | std_logic_vector ( 9 downto 0 ) |

| Temperature sens. 2. | |

| al_dig_u_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro dig. | |

| al_ana_u_r | std_logic_vector ( 9 downto 0 ) |

| U 2.5 altro analog. | |

| t4_th_r | std_logic_vector ( 9 downto 0 ) |

| Th: Forth ADC T. | |

| va_rec_up_th_r | std_logic_vector ( 9 downto 0 ) |

| Th: U 2.5 VA (m). | |

| va_sup_up_th_r | std_logic_vector ( 9 downto 0 ) |

| Th: U 1.5 VA (m). | |

| va_sup_um_th_r | std_logic_vector ( 9 downto 0 ) |

| Th: U -2.0 VA (m). | |

| va_rec_um_th_r | std_logic_vector ( 9 downto 0 ) |

| Th: U -2.0 (m). | |

| t4_r | std_logic_vector ( 9 downto 0 ) |

| Cu: Forth ADC T. | |

| va_rec_up_r | std_logic_vector ( 9 downto 0 ) |

| Cu: U 2.5 VA (m). | |

| va_sup_up_r | std_logic_vector ( 9 downto 0 ) |

| Cu: U 1.5 VA (m). | |

| va_sup_um_r | std_logic_vector ( 9 downto 0 ) |

| Cu: U -2.0 VA (m). | |

| va_rec_um_r | std_logic_vector ( 9 downto 0 ) |

| Cu: U -2.0 (m). | |

| l1cnt_r | std_logic_vector ( 15 downto 0 ) |

| L1 counter. | |

| l2cnt_r | std_logic_vector ( 15 downto 0 ) |

| L2 counter. | |

| sclkcnt_r | std_logic_vector ( 15 downto 0 ) |

| Slow clock counter. | |

| dstbcnt_r | std_logic_vector ( 7 downto 0 ) |

| Data strobe counter. | |

| tsm_word_r | std_logic_vector ( 8 downto 0 ) |

| Test mode words. | |

| us_ratio_r | std_logic_vector ( 15 downto 0 ) |

| Under sampling ra. | |

| csr0_r | std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) |

| csr1_r | std_logic_vector ( 13 downto 0 ) := ( others = > ' 0 ' ) |

| csr2_r | std_logic_vector ( 15 downto 0 ) |

| Config/Status 2. | |

| csr3_r | std_logic_vector ( 15 downto 0 ) |

| Config/Status 3. | |

| fmdd_stat_r | std_logic_vector ( 15 downto 0 ) |

| FMDD status. | |

| l0cnt_r | std_logic_vector ( 15 downto 0 ) |

| L0 counters. | |

| hold_wait_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Wait to hold. | |

| l1_timeout_r | std_logic_vector ( 15 downto 0 ) |

| FMD: L1 timeout. | |

| l2_timeout_r | std_logic_vector ( 15 downto 0 ) |

| FMD: L2 timeout. | |

| shift_div_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Shift clk. | |

| strips_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Strips. | |

| cal_level_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Cal pulse. | |

| cal_iter_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Cal events. | |

| shape_bias_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Shape bias. | |

| vfs_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Shape ref. | |

| vfp_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Preamp ref. | |

| sample_div_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Sample clk. | |

| fmdd_cmd_r | std_logic_vector ( 15 downto 0 ) |

| FMD: Commands. | |

| mebs_r | std_logic_vector ( 8 downto 0 ) |

| MEB config. | |

| cal_delay_r | std_logic_vector ( 15 downto 0 ) |

| CAL xtra delay. | |

| cnv_mode_i | std_logic |

| bc_error_i | std_logic |

| bc_int_i | std_logic |

| meb_cnt_i | std_logic_vector ( 3 downto 0 ) |

| csr1_ii | std_logic_vector ( 13 downto 0 ) |

| Config/Status 1. | |

| csr1_clrrst_i | std_logic |

| ints_i | std_logic_vector ( 19 downto 0 ) |

Component Instantiations | |

| t1_ms | int_mstable <Entity int_mstable> |

| t2_ms | int_mstable <Entity int_mstable> |

| t3_ms | int_mstable <Entity int_mstable> |

| t4_ms | int_mstable <Entity int_mstable> |

| t1sens_ms | int_mstable <Entity int_mstable> |

| t2sens_ms | int_mstable <Entity int_mstable> |

| al_ana_i_ms | int_mstable <Entity int_mstable> |

| va_sup_ip_ms | int_mstable <Entity int_mstable> |

| va_rec_im_ms | int_mstable <Entity int_mstable> |

| va_sup_im_ms | int_mstable <Entity int_mstable> |

| al_dig_i_ms | int_mstable <Entity int_mstable> |

| flash_i_ms | int_mstable <Entity int_mstable> |

| va_rec_ip_ms | int_mstable <Entity int_mstable> |

| va_sup_um_ms | int_mstable <Entity int_mstable> |

| va_rec_um_ms | int_mstable <Entity int_mstable> |

| al_ana_u_ms | int_mstable <Entity int_mstable> |

| va_sup_up_ms | int_mstable <Entity int_mstable> |

| gtl_u_ms | int_mstable <Entity int_mstable> |

| al_dig_u_ms | int_mstable <Entity int_mstable> |

| va_rec_up_ms | int_mstable <Entity int_mstable> |

Member Function Documentation

| adc_register | ( clk , | |

| rstb ) |

| ans_cmds | ( clk , | |

| rstb ) |

| errors | ( clk , | |

| rstb ) |

| output_al | ( clk ) |

| output_sc | ( clk ) |

| reg_register | ( clk , | |

| rstb ) |

Member Data Documentation

al_ana_i_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro ana.

al_ana_i_ms int_mstable [Component Instantiation] |

al_ana_i_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro ana.

al_ana_i_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro ana.

al_ana_i_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro ana.

al_ana_u_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro ana.

al_ana_u_ms int_mstable [Component Instantiation] |

al_ana_u_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro analog.

al_ana_u_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro ana.

al_ana_u_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro analog.

al_dig_i_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro dig.

al_dig_i_ms int_mstable [Component Instantiation] |

al_dig_i_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro dig.

al_dig_i_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro dig.

al_dig_i_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V altro dig.

al_dig_u_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro dig.

al_dig_u_ms int_mstable [Component Instantiation] |

al_dig_u_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro dig.

al_dig_u_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro dig.

al_dig_u_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 altro dig.

AUTO_CLEAR boolean := true [Constant] |

bc_error_i std_logic [Signal] |

bc_int_i std_logic [Signal] |

cal_delay_i std_logic_vector ( 15 downto 0 ) [Signal] |

CAL xtra delay.

cal_delay_r std_logic_vector ( 15 downto 0 ) [Signal] |

CAL xtra delay.

cal_iter_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Cal events.

cal_iter_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Cal events.

cal_level_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Cal pulse.

cal_level_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Cal pulse.

cnv_mode_i std_logic [Signal] |

csr0_i std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

csr0_r std_logic_vector ( 10 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

csr1_clrrst_i std_logic [Signal] |

csr1_i std_logic_vector ( 13 downto 0 ) [Signal] |

Config/Status 1.

csr1_ii std_logic_vector ( 13 downto 0 ) [Signal] |

Config/Status 1.

csr1_r std_logic_vector ( 13 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

csr2_i std_logic_vector ( 15 downto 0 ) [Signal] |

Config/Status 2.

csr2_r std_logic_vector ( 15 downto 0 ) [Signal] |

Config/Status 2.

csr3_i std_logic_vector ( 15 downto 0 ) [Signal] |

Config/Status 3.

csr3_r std_logic_vector ( 15 downto 0 ) [Signal] |

Config/Status 3.

dstbcnt_r std_logic_vector ( 7 downto 0 ) [Signal] |

Data strobe counter.

flash_i_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 3.3 V.

flash_i_ms int_mstable [Component Instantiation] |

flash_i_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 3.3 V.

flash_i_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 3.3 V.

flash_i_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 3.3 V.

fmdd_cmd_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Commands.

fmdd_cmd_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Commands.

fmdd_stat_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMDD status.

gtl_u_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 V Digital.

gtl_u_ms int_mstable [Component Instantiation] |

gtl_u_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 V Digital.

gtl_u_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 V Digital.

gtl_u_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 V Digital.

hold_wait_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Wait to hold.

hold_wait_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Wait to hold.

INT_TIMES integer := 2 [Constant] |

ints_i std_logic_vector ( 19 downto 0 ) [Signal] |

l0cnt_i std_logic_vector ( 15 downto 0 ) [Signal] |

L0 counters.

l0cnt_r std_logic_vector ( 15 downto 0 ) [Signal] |

L0 counters.

l1_timeout_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: L1 timeout.

l1_timeout_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: L1 timeout.

l1cnt_i std_logic_vector ( 15 downto 0 ) [Signal] |

L1 counter.

l1cnt_r std_logic_vector ( 15 downto 0 ) [Signal] |

L1 counter.

l2_timeout_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: L2 timeout.

l2_timeout_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: L2 timeout.

l2cnt_i std_logic_vector ( 15 downto 0 ) [Signal] |

L2 counter.

l2cnt_r std_logic_vector ( 15 downto 0 ) [Signal] |

L2 counter.

meb_cnt_i std_logic_vector ( 3 downto 0 ) [Signal] |

mebs_i std_logic_vector ( 4 downto 0 ) [Signal] |

MEB config.

mebs_r std_logic_vector ( 8 downto 0 ) [Signal] |

MEB config.

sample_div_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Sample clk.

sample_div_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Sample clk.

sclkcnt_i std_logic_vector ( 15 downto 0 ) [Signal] |

Slow clock counter.

sclkcnt_r std_logic_vector ( 15 downto 0 ) [Signal] |

Slow clock counter.

shape_bias_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shape bias.

shape_bias_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shape bias.

shift_div_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shift clk.

shift_div_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shift clk.

strips_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Strips.

strips_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Strips.

t1_i std_logic_vector ( 9 downto 0 ) [Signal] |

First ADC T.

t1_ms int_mstable [Component Instantiation] |

t1_r std_logic_vector ( 9 downto 0 ) [Signal] |

First ADC T.

t1_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

First ADC T.

t1_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

First ADC T.

t1sens_i std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 1.

t1sens_ms int_mstable [Component Instantiation] |

t1sens_r std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 1.

t1sens_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 1.

t1sens_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 1.

t2_i std_logic_vector ( 9 downto 0 ) [Signal] |

Second ADC T.

t2_ms int_mstable [Component Instantiation] |

t2_r std_logic_vector ( 9 downto 0 ) [Signal] |

Second ADC T.

t2_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

Second ADC T.

t2_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Second ADC T.

t2sens_i std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 2.

t2sens_ms int_mstable [Component Instantiation] |

t2sens_r std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 2.

t2sens_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 2.

t2sens_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Temperature sens. 2.

t3_i std_logic_vector ( 9 downto 0 ) [Signal] |

Third ADC T.

t3_ms int_mstable [Component Instantiation] |

t3_r std_logic_vector ( 9 downto 0 ) [Signal] |

Third ADC T.

t3_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

Third ADC T.

t3_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Third ADC T.

t4_i std_logic_vector ( 9 downto 0 ) [Signal] |

Forth ADC T.

t4_ms int_mstable [Component Instantiation] |

t4_r std_logic_vector ( 9 downto 0 ) [Signal] |

Cu: Forth ADC T.

t4_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

Forth ADC T.

t4_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Th: Forth ADC T.

tsm_word_i std_logic_vector ( 8 downto 0 ) [Signal] |

Test mode words.

tsm_word_r std_logic_vector ( 8 downto 0 ) [Signal] |

Test mode words.

us_ratio_i std_logic_vector ( 15 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

us_ratio_r std_logic_vector ( 15 downto 0 ) [Signal] |

Under sampling ra.

va_rec_im_i std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V.

va_rec_im_ms int_mstable [Component Instantiation] |

va_rec_im_r std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V.

va_rec_im_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V.

va_rec_im_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V.

va_rec_ip_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V VA.

va_rec_ip_ms int_mstable [Component Instantiation] |

va_rec_ip_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V VA.

va_rec_ip_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V VA.

va_rec_ip_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 2.5 V VA.

va_rec_um_i std_logic_vector ( 9 downto 0 ) [Signal] |

U -2.0 (m).

va_rec_um_ms int_mstable [Component Instantiation] |

va_rec_um_r std_logic_vector ( 9 downto 0 ) [Signal] |

Cu: U -2.0 (m).

va_rec_um_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U -2.0 (m).

va_rec_um_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Th: U -2.0 (m).

va_rec_up_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 VA (m).

va_rec_up_ms int_mstable [Component Instantiation] |

va_rec_up_r std_logic_vector ( 9 downto 0 ) [Signal] |

Cu: U 2.5 VA (m).

va_rec_up_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 2.5 VA (m).

va_rec_up_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Th: U 2.5 VA (m).

va_sup_im_i std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V VA.

va_sup_im_ms int_mstable [Component Instantiation] |

va_sup_im_r std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V VA.

va_sup_im_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V VA.

va_sup_im_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I -2.0 V VA.

va_sup_ip_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 1.5 V VA.

va_sup_ip_ms int_mstable [Component Instantiation] |

va_sup_ip_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 1.5 V VA.

va_sup_ip_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

I 1.5 V VA.

va_sup_ip_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

I 1.5 V VA.

va_sup_um_i std_logic_vector ( 9 downto 0 ) [Signal] |

U -2.0 VA (m).

va_sup_um_ms int_mstable [Component Instantiation] |

va_sup_um_r std_logic_vector ( 9 downto 0 ) [Signal] |

Cu: U -2.0 VA (m).

va_sup_um_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U -2.0 VA (m).

va_sup_um_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Th: U -2.0 VA (m).

va_sup_up_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 1.5 VA (m).

va_sup_up_ms int_mstable [Component Instantiation] |

va_sup_up_r std_logic_vector ( 9 downto 0 ) [Signal] |

Cu: U 1.5 VA (m).

va_sup_up_th_i std_logic_vector ( 9 downto 0 ) [Signal] |

U 1.5 VA (m).

va_sup_up_th_r std_logic_vector ( 9 downto 0 ) [Signal] |

Th: U 1.5 VA (m).

vfp_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Preamp ref.

vfp_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Preamp ref.

vfs_i std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shape ref.

vfs_r std_logic_vector ( 15 downto 0 ) [Signal] |

FMD: Shape ref.

The documentation for this class was generated from the following file:

- bc/bc_core/registers/registers_block/registers_block.vhd

1.6.2-20100208

1.6.2-20100208