pipe_stim Architecture Reference

Inheritance diagram for pipe_stim:

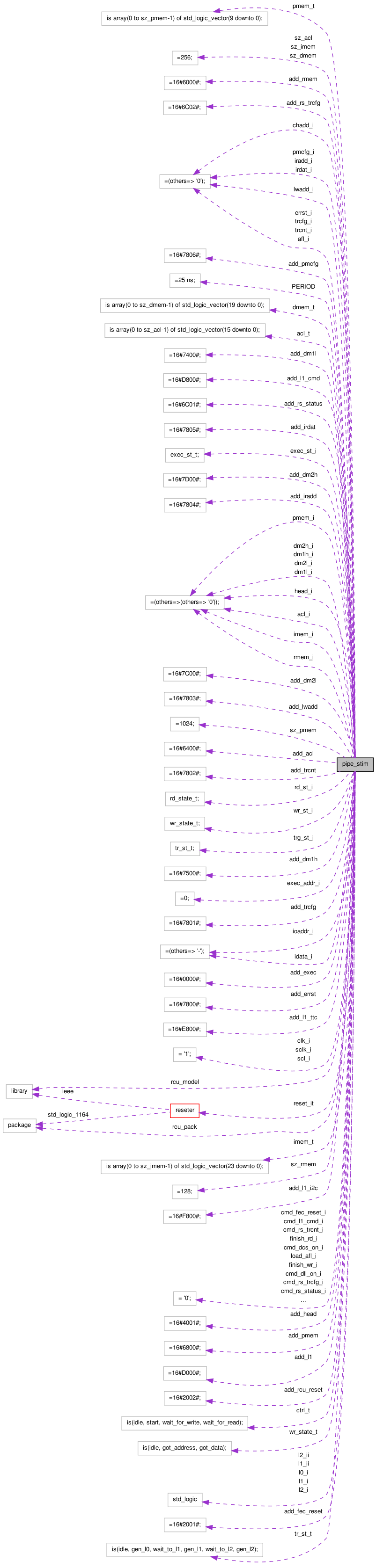

Collaboration diagram for pipe_stim:

Functions | |

| string | slv2str ( constant v: in std_logic_vector ) |

| std_logic_vector | hex2quad ( constant x: in character ) |

| std_logic_vector | hstr2slv ( constant x: in string ) |

| character | quad2hex ( constant q: in std_logic_vector(0 to 3) ) |

| string | slv2hstr ( constant v: in std_logic_vector ) |

| integer | slv2int ( constant x: in std_logic_vector ) |

| std_logic_vector | int2slv ( constant x: in integer , constant l: in natural ) |

| std_logic | parity ( constant x: in std_logic_vector ) |

Processes | |

| stimuli | ( ) |

| control | ( clk_i , grst_i ) |

| writer | ( clk_i , grst_i ) |

| reader | ( clk_i , grst_i ) |

| imem_exec | ( clk_i , grst_i ) |

| registers | ( clk_i , grst_i ) |

| triggers | ( clk_i , grst_i ) |

Procedures | |

| read_what( file input: text ,variable what: out character ) | |

| read_addr_data( file input: text variable what: out character variable addr: out string ( 1 to 7 ) variable data: out string ( 1 to 10 ) ) | |

Libraries | |

| rcu_model | |

Packages | |

| rcu_pack | Package <rcu_pack> |

Constants | |

| PERIOD | time := 25 ns |

| SIZE | integer := 8 |

| add_errst | integer := 16#7800# |

| add_trcfg | integer := 16#7801# |

| add_trcnt | integer := 16#7802# |

| add_lwadd | integer := 16#7803# |

| add_iradd | integer := 16#7804# |

| add_irdat | integer := 16#7805# |

| add_pmcfg | integer := 16#7806# |

| add_chadd | integer := 16#7807# |

| add_afl | integer := 16#8000# |

| add_rs_status | integer := 16#6C01# |

| add_rs_trcfg | integer := 16#6C02# |

| add_rs_trcnt | integer := 16#6C03# |

| add_rs_buf1 | integer := 16#6C04# |

| add_rs_buf2 | integer := 16#6C05# |

| add_exec | integer := 16#0000# |

| add_abort | integer := 16#0800# |

| add_dcs_on | integer := 16#E000# |

| add_dll_on | integer := 16#F000# |

| add_l1_ttc | integer := 16#E800# |

| add_l1_i2c | integer := 16#F800# |

| add_l1_cmd | integer := 16#D800# |

| add_l1 | integer := 16#D000# |

| add_glb_reset | integer := 16#2000# |

| add_fec_reset | integer := 16#2001# |

| add_rcu_reset | integer := 16#2002# |

| add_imem | integer := 16#7000# |

| add_pmem | integer := 16#6800# |

| add_rmem | integer := 16#6000# |

| add_acl | integer := 16#6400# |

| add_dm1l | integer := 16#7400# |

| add_dm1h | integer := 16#7500# |

| add_dm2l | integer := 16#7C00# |

| add_dm2h | integer := 16#7D00# |

| add_head | integer := 16#4001# |

| sz_imem | integer := 256 |

| sz_pmem | integer := 1024 |

| sz_rmem | integer := 128 |

| sz_acl | integer := 256 |

| sz_dmem | integer := 256 |

| sz_head | integer := 8 |

Types | |

| wr_state_t | ( idle , got_address , got_data ) |

| rd_state_t | ( idle , got_address , start , output , endit ) |

| ctrl_t | ( idle , start , wait_for_write , wait_for_read ) |

| exec_st_t | ( idle , start , next_instr , rcu_instr , wait_clk , altro_instr , altro_instr2 , set_bus , strobe , wait_strobe , wait_ack , take_data ) |

| tr_st_t | ( idle , gen_l0 , wait_to_l1 , gen_l1 , wait_to_l2 , gen_l2 ) |

| imem_t | array ( 0 to sz_imem -1 ) of std_logic_vector ( 23 downto 0 ) |

| pmem_t | array ( 0 to sz_pmem -1 ) of std_logic_vector ( 9 downto 0 ) |

| rmem_t | array ( 0 to sz_rmem -1 ) of std_logic_vector ( 19 downto 0 ) |

| acl_t | array ( 0 to sz_acl -1 ) of std_logic_vector ( 15 downto 0 ) |

| dmem_t | array ( 0 to sz_dmem -1 ) of std_logic_vector ( 19 downto 0 ) |

| head_t | array ( 0 to sz_head -1 ) of std_logic_vector ( 31 downto 0 ) |

Signals | |

| clk_i | std_logic := ' 1 ' |

| sclk_i | std_logic := ' 1 ' |

| scl_i | std_logic := ' 1 ' |

| grst_i | std_logic := ' 0 ' |

| l0_i | std_logic |

| l1_i | std_logic |

| l2_i | std_logic |

| l1_ii | std_logic |

| l2_ii | std_logic |

| done_i | boolean := false |

| trg_st_i | tr_st_t |

| exec_st_i | exec_st_t |

| wr_st_i | wr_state_t |

| rd_st_i | rd_state_t |

| ctrl_st_i | ctrl_t |

| enable_rd_i | std_logic := ' 0 ' |

| enable_wr_i | std_logic := ' 0 ' |

| finish_rd_i | std_logic := ' 0 ' |

| finish_wr_i | std_logic := ' 0 ' |

| enable_out_i | std_logic := ' 0 ' |

| timeout_i | std_logic := ' 0 ' |

| ioaddr_i | std_logic_vector ( 19 downto 0 ) := ( others = > ' - ' ) |

| idata_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' - ' ) |

| errst_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| trcfg_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| trcnt_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| lwadd_i | std_logic_vector ( 17 downto 0 ) := ( others = > ' 0 ' ) |

| iradd_i | std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) |

| irdat_i | std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) |

| pmcfg_i | std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) |

| chadd_i | std_logic_vector ( 23 downto 0 ) := ( others = > ' 0 ' ) |

| afl_i | std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) |

| load_trcfg_i | std_logic := ' 0 ' |

| load_pmcfg_i | std_logic := ' 0 ' |

| load_afl_i | std_logic := ' 0 ' |

| exec_addr_i | integer := 0 |

| cmd_rs_status_i | std_logic := ' 0 ' |

| cmd_rs_trcfg_i | std_logic := ' 0 ' |

| cmd_rs_trcnt_i | std_logic := ' 0 ' |

| cmd_rs_buf1_i | std_logic := ' 0 ' |

| cmd_rs_buf2_i | std_logic := ' 0 ' |

| cmd_exec_i | std_logic := ' 0 ' |

| cmd_abort_i | std_logic := ' 0 ' |

| exec_busy_i | std_logic := ' 0 ' |

| cmd_dcs_on_i | std_logic := ' 0 ' |

| cmd_dll_on_i | std_logic := ' 0 ' |

| cmd_l1_ttc_i | std_logic := ' 0 ' |

| cmd_l1_i2c_i | std_logic := ' 0 ' |

| cmd_l1_cmd_i | std_logic := ' 0 ' |

| cmd_l1_i | std_logic := ' 0 ' |

| cmd_glb_reset_i | std_logic := ' 0 ' |

| cmd_fec_reset_i | std_logic := ' 0 ' |

| cmd_rcu_reset_i | std_logic := ' 0 ' |

| icmd_rs_trcfg_i | std_logic := ' 0 ' |

| icmd_rs_status_i | std_logic := ' 0 ' |

| icmd_rs_trcnt_i | std_logic := ' 0 ' |

| icmd_trigger_i | std_logic := ' 0 ' |

| imem_i | imem_t := ( others = > ( others = > ' 0 ' ) ) |

| pmem_i | pmem_t := ( others = > ( others = > ' 0 ' ) ) |

| rmem_i | rmem_t := ( others = > ( others = > ' 0 ' ) ) |

| acl_i | acl_t := ( others = > ( others = > ' 0 ' ) ) |

| dm1l_i | dmem_t := ( others = > ( others = > ' 0 ' ) ) |

| dm1h_i | dmem_t := ( others = > ( others = > ' 0 ' ) ) |

| dm2l_i | dmem_t := ( others = > ( others = > ' 0 ' ) ) |

| dm2h_i | dmem_t := ( others = > ( others = > ' 0 ' ) ) |

| head_i | head_t := ( others = > ( others = > ' 0 ' ) ) |

Component Instantiations | |

| reset_it | reseter <Entity reseter> |

| rclk_clocker | clocker <Entity clocker> |

| sclk_clocker | clocker <Entity clocker> |

Member Function Documentation

| control | ( clk_i , | |

| grst_i ) |

| std_logic_vector hex2quad | (constant x in character ) |

| std_logic_vector hstr2slv | (constant x in string ) |

| imem_exec | ( clk_i , | |

| grst_i ) |

| std_logic_vector int2slv | (constant x in integer , | |

| constant l in natural ) |

| std_logic parity | (constant x in std_logic_vector ) |

| character quad2hex | (constant q in std_logic_vector(0 to 3) ) |

| read_addr_data | (file input text text , | |

| variable what out character , | ||

| variable addr out string(1 to 7) , | ||

| variable data out string(1 to 10) ) |

| read_what | (file input text text , | |

| variable what out character ) |

| reader | ( clk_i , | |

| grst_i ) |

| registers | ( clk_i , | |

| grst_i ) |

| string slv2hstr | (constant v in std_logic_vector ) |

| integer slv2int | (constant x in std_logic_vector ) |

| string slv2str | (constant v in std_logic_vector ) |

stimuli ( ) [Process] |

| triggers | ( clk_i , | |

| grst_i ) |

| writer | ( clk_i , | |

| grst_i ) |

Member Data Documentation

add_abort integer := 16#0800# [Constant] |

add_acl integer := 16#6400# [Constant] |

add_afl integer := 16#8000# [Constant] |

add_chadd integer := 16#7807# [Constant] |

add_dcs_on integer := 16#E000# [Constant] |

add_dll_on integer := 16#F000# [Constant] |

add_dm1h integer := 16#7500# [Constant] |

add_dm1l integer := 16#7400# [Constant] |

add_dm2h integer := 16#7D00# [Constant] |

add_dm2l integer := 16#7C00# [Constant] |

add_errst integer := 16#7800# [Constant] |

add_exec integer := 16#0000# [Constant] |

add_fec_reset integer := 16#2001# [Constant] |

add_glb_reset integer := 16#2000# [Constant] |

add_head integer := 16#4001# [Constant] |

add_imem integer := 16#7000# [Constant] |

add_iradd integer := 16#7804# [Constant] |

add_irdat integer := 16#7805# [Constant] |

add_l1 integer := 16#D000# [Constant] |

add_l1_cmd integer := 16#D800# [Constant] |

add_l1_i2c integer := 16#F800# [Constant] |

add_l1_ttc integer := 16#E800# [Constant] |

add_lwadd integer := 16#7803# [Constant] |

add_pmcfg integer := 16#7806# [Constant] |

add_pmem integer := 16#6800# [Constant] |

add_rcu_reset integer := 16#2002# [Constant] |

add_rmem integer := 16#6000# [Constant] |

add_rs_buf1 integer := 16#6C04# [Constant] |

add_rs_buf2 integer := 16#6C05# [Constant] |

add_rs_status integer := 16#6C01# [Constant] |

add_rs_trcfg integer := 16#6C02# [Constant] |

add_rs_trcnt integer := 16#6C03# [Constant] |

add_trcfg integer := 16#7801# [Constant] |

add_trcnt integer := 16#7802# [Constant] |

afl_i std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

chadd_i std_logic_vector ( 23 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

clk_i std_logic := ' 1 ' [Signal] |

cmd_abort_i std_logic := ' 0 ' [Signal] |

cmd_dcs_on_i std_logic := ' 0 ' [Signal] |

cmd_dll_on_i std_logic := ' 0 ' [Signal] |

cmd_exec_i std_logic := ' 0 ' [Signal] |

cmd_fec_reset_i std_logic := ' 0 ' [Signal] |

cmd_glb_reset_i std_logic := ' 0 ' [Signal] |

cmd_l1_cmd_i std_logic := ' 0 ' [Signal] |

cmd_l1_i std_logic := ' 0 ' [Signal] |

cmd_l1_i2c_i std_logic := ' 0 ' [Signal] |

cmd_l1_ttc_i std_logic := ' 0 ' [Signal] |

cmd_rcu_reset_i std_logic := ' 0 ' [Signal] |

cmd_rs_buf1_i std_logic := ' 0 ' [Signal] |

cmd_rs_buf2_i std_logic := ' 0 ' [Signal] |

cmd_rs_status_i std_logic := ' 0 ' [Signal] |

cmd_rs_trcfg_i std_logic := ' 0 ' [Signal] |

cmd_rs_trcnt_i std_logic := ' 0 ' [Signal] |

ctrl_t ( idle , start , wait_for_write , wait_for_read ) [Type] |

done_i boolean := false [Signal] |

enable_out_i std_logic := ' 0 ' [Signal] |

enable_rd_i std_logic := ' 0 ' [Signal] |

enable_wr_i std_logic := ' 0 ' [Signal] |

errst_i std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

exec_addr_i integer := 0 [Signal] |

exec_busy_i std_logic := ' 0 ' [Signal] |

exec_st_t ( idle , start , next_instr , rcu_instr , wait_clk , altro_instr , altro_instr2 , set_bus , strobe , wait_strobe , wait_ack , take_data ) [Type] |

finish_rd_i std_logic := ' 0 ' [Signal] |

finish_wr_i std_logic := ' 0 ' [Signal] |

grst_i std_logic := ' 0 ' [Signal] |

icmd_rs_status_i std_logic := ' 0 ' [Signal] |

icmd_rs_trcfg_i std_logic := ' 0 ' [Signal] |

icmd_rs_trcnt_i std_logic := ' 0 ' [Signal] |

icmd_trigger_i std_logic := ' 0 ' [Signal] |

idata_i std_logic_vector ( 31 downto 0 ) := ( others = > ' - ' ) [Signal] |

ioaddr_i std_logic_vector ( 19 downto 0 ) := ( others = > ' - ' ) [Signal] |

iradd_i std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

irdat_i std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

l0_i std_logic [Signal] |

l1_i std_logic [Signal] |

l1_ii std_logic [Signal] |

l2_i std_logic [Signal] |

l2_ii std_logic [Signal] |

load_afl_i std_logic := ' 0 ' [Signal] |

load_pmcfg_i std_logic := ' 0 ' [Signal] |

load_trcfg_i std_logic := ' 0 ' [Signal] |

lwadd_i std_logic_vector ( 17 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

PERIOD time := 25 ns [Constant] |

pmcfg_i std_logic_vector ( 19 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

rclk_clocker clocker [Component Instantiation] |

rcu_pack package [Package] |

rd_st_i rd_state_t [Signal] |

rd_state_t ( idle , got_address , start , output , endit ) [Type] |

scl_i std_logic := ' 1 ' [Signal] |

sclk_clocker clocker [Component Instantiation] |

sclk_i std_logic := ' 1 ' [Signal] |

SIZE integer := 8 [Constant] |

sz_acl integer := 256 [Constant] |

sz_dmem integer := 256 [Constant] |

sz_head integer := 8 [Constant] |

sz_imem integer := 256 [Constant] |

sz_pmem integer := 1024 [Constant] |

sz_rmem integer := 128 [Constant] |

timeout_i std_logic := ' 0 ' [Signal] |

tr_st_t ( idle , gen_l0 , wait_to_l1 , gen_l1 , wait_to_l2 , gen_l2 ) [Type] |

trcfg_i std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

trcnt_i std_logic_vector ( 31 downto 0 ) := ( others = > ' 0 ' ) [Signal] |

wr_st_i wr_state_t [Signal] |

wr_state_t ( idle , got_address , got_data ) [Type] |

The documentation for this class was generated from the following file:

- rcu/rcu_pipe.vhd

1.6.2-20100208

1.6.2-20100208