rtl5 Architecture Reference

Inheritance diagram for rtl5:

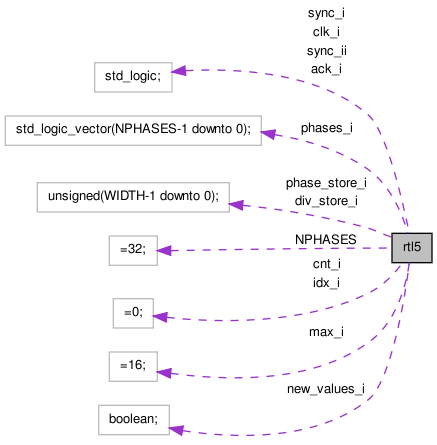

Collaboration diagram for rtl5:

Processes | |

| store_values | ( clk , rstb ) |

| clk_gen | ( clk , rstb ) |

| phase_gen | ( clk ) |

Constants | |

| NPHASES | integer := 32 |

Signals | |

| phase_store_i | unsigned ( WIDTH-1 downto 0 ) |

| div_store_i | unsigned ( WIDTH-1 downto 0 ) |

| new_values_i | boolean |

| cnt_i | integer range 0 to 2 **WIDTH := 0 |

| max_i | integer range 0 to 2 **WIDTH := 16 |

| idx_i | integer range 0 to 2 **WIDTH := 0 |

| phases_i | std_logic_vector ( NPHASES -1 downto 0 ) |

| clk_i | std_logic |

| sync_i | std_logic |

| sync_ii | std_logic |

| ack_i | std_logic |

Member Function Documentation

| clk_gen | ( clk , | |

| rstb ) |

| phase_gen | ( clk ) |

| store_values | ( clk , | |

| rstb ) |

Member Data Documentation

ack_i std_logic [Signal] |

clk_i std_logic [Signal] |

cnt_i integer range 0 to 2 **WIDTH := 0 [Signal] |

div_store_i unsigned ( WIDTH-1 downto 0 ) [Signal] |

idx_i integer range 0 to 2 **WIDTH := 0 [Signal] |

max_i integer range 0 to 2 **WIDTH := 16 [Signal] |

new_values_i boolean [Signal] |

NPHASES integer := 32 [Constant] |

phase_store_i unsigned ( WIDTH-1 downto 0 ) [Signal] |

sync_i std_logic [Signal] |

sync_ii std_logic [Signal] |

The documentation for this class was generated from the following file:

- bc/fmdd/clock_gen/clock_gen.vhd

1.6.2-20100208

1.6.2-20100208