rtl Architecture Reference

[Model of ALTRO chip]

Inheritance diagram for rtl:

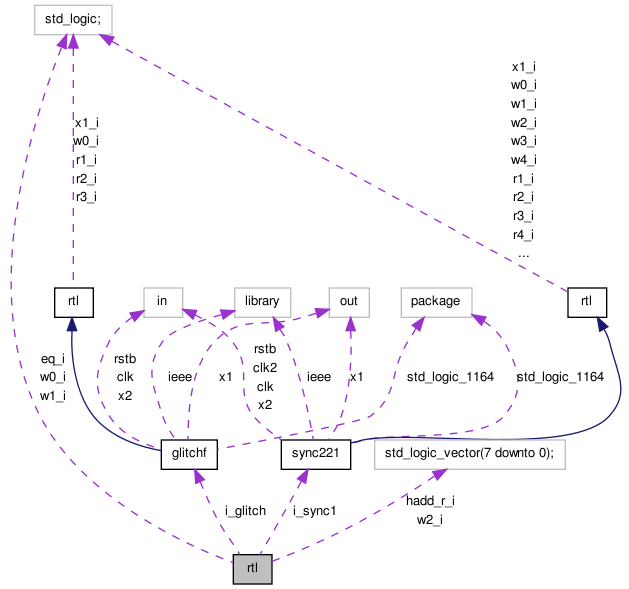

Collaboration diagram for rtl:

Processes | |

| p_busFFF | ( clk2 , rstb ) |

Signals | |

| eq_i | std_logic |

| Equal. | |

| w1_i | std_logic |

| Wire 1. | |

| w0_i | std_logic |

| Wire 0. | |

| w2_i | std_logic_vector ( 7 downto 0 ) |

| wire 2 | |

| hadd_r_i | std_logic_vector ( 7 downto 0 ) |

| hardware address | |

Component Instantiations | |

| i_glitch | glitchf <Entity glitchf> |

| Trigger glitch filter. | |

| i_sync1 | sync221 <Entity sync221> |

| Sync l2 to both clocks. | |

Detailed Description

Architecture of bus interface

Member Function Documentation

| p_busFFF | ( clk2 , | |

| rstb ) |

Decode address

- Parameters:

-

clk2 Clock rstb Async reset

Member Data Documentation

eq_i std_logic [Signal] |

Equal.

hadd_r_i std_logic_vector ( 7 downto 0 ) [Signal] |

hardware address

w0_i std_logic [Signal] |

Wire 0.

w1_i std_logic [Signal] |

Wire 1.

w2_i std_logic_vector ( 7 downto 0 ) [Signal] |

wire 2

The documentation for this class was generated from the following file:

- altro/busint.vhd

1.6.2-20100208

1.6.2-20100208