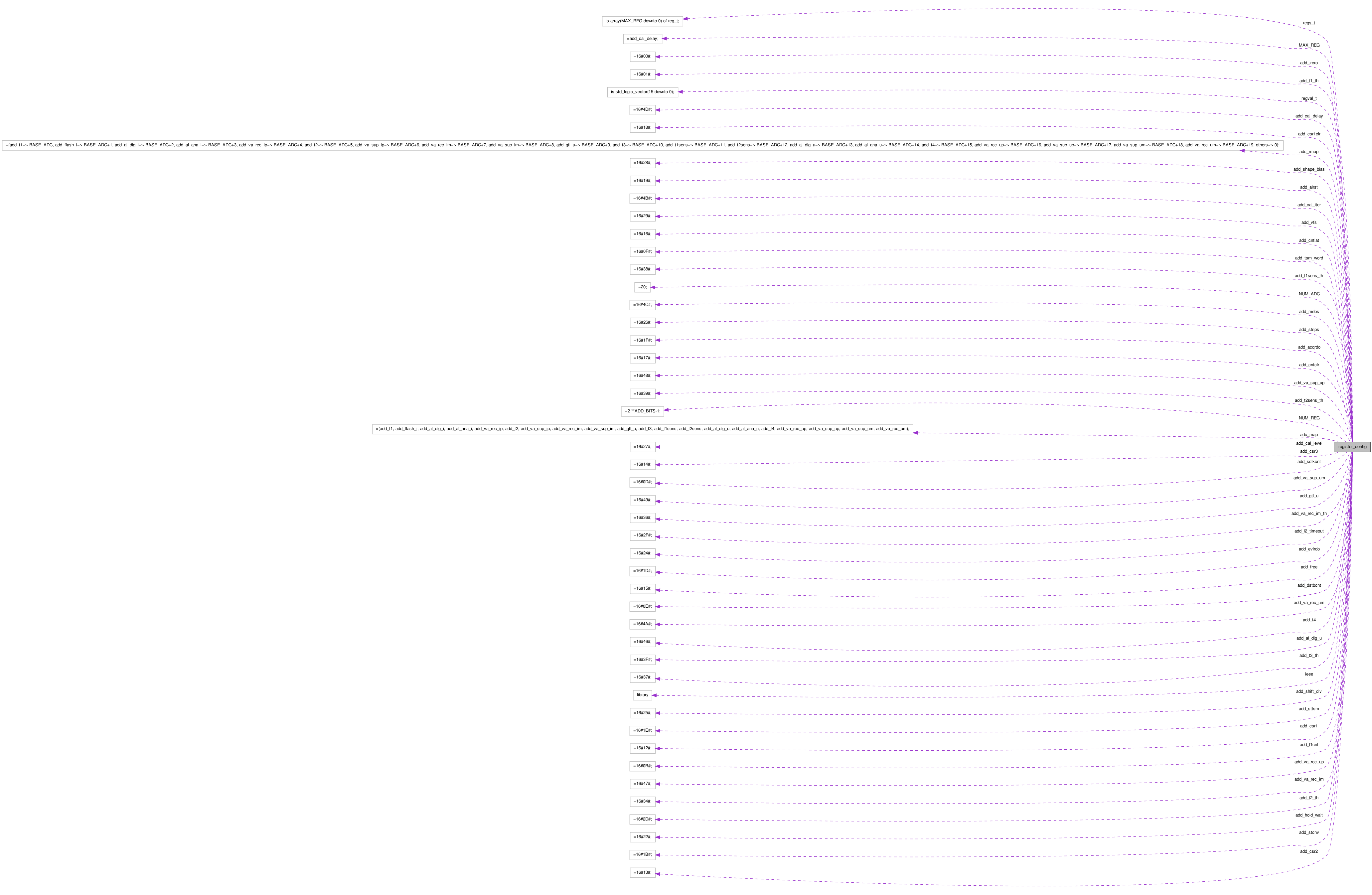

register_config Package Reference

[Registers]

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

| numeric_std | |

Constants | |

| version | std_logic_vector ( 15 downto 0 ) := X " 0220 " |

| Version number X"0113" -> Major: 0x01, minor: 0x13=19 Version number. | |

| ADD_BITS | integer := 7 |

| Number of addrss bits. | |

| NUM_REG | integer := 2 **ADD_BITS -1 |

| Number of registers. | |

| add_zero | add_t := 16#00# |

| add_t1_th | add_t := 16#01# |

| First ADC T. | |

| add_flash_i_th | add_t := 16#02# |

| I 3.3 V. | |

| add_al_dig_i_th | add_t := 16#03# |

| I 2.5 V altro digital. | |

| add_al_ana_i_th | add_t := 16#04# |

| I 2.5 V altro analog. | |

| add_va_rec_ip_th | add_t := 16#05# |

| I 2.5 V VA. | |

| add_t1 | add_t := 16#06# |

| First ADC T. | |

| add_flash_i | add_t := 16#07# |

| I 3.3 V. | |

| add_al_dig_i | add_t := 16#08# |

| I 2.5 V altro digital. | |

| add_al_ana_i | add_t := 16#09# |

| I 2.5 V altro analog. | |

| add_va_rec_ip | add_t := 16#0A# |

| I 2.5 V VA. | |

| add_t2_th | add_t := 16#2D# |

| Second ADC T. | |

| add_va_sup_ip_th | add_t := 16#2E# |

| I 1.5 V VA. | |

| add_va_rec_im_th | add_t := 16#2F# |

| I -2.0 V. | |

| add_va_sup_im_th | add_t := 16#30# |

| I -2.0 V VA. | |

| add_gtl_u_th | add_t := 16#31# |

| 2.5 V Digital driver | |

| add_t2 | add_t := 16#32# |

| Second ADC T. | |

| add_va_sup_ip | add_t := 16#33# |

| I 1.5 V VA. | |

| add_va_rec_im | add_t := 16#34# |

| I -2.0 V. | |

| add_va_sup_im | add_t := 16#35# |

| I -2.0 V VA. | |

| add_gtl_u | add_t := 16#36# |

| 2.5 V Digital driver | |

| add_t3_th | add_t := 16#37# |

| Third ADC T. | |

| add_t1sens_th | add_t := 16#38# |

| Temperature sens. 1. | |

| add_t2sens_th | add_t := 16#39# |

| Temperature sens. 2. | |

| add_al_dig_u_th | add_t := 16#3A# |

| U 2.5 altro digital (m). | |

| add_al_ana_u_th | add_t := 16#3B# |

| U 2.5 altro analog (m). | |

| add_t3 | add_t := 16#3C# |

| Third ADC T. | |

| add_t1sens | add_t := 16#3D# |

| Temperature sens. 1. | |

| add_t2sens | add_t := 16#3E# |

| Temperature sens. 2. | |

| add_al_dig_u | add_t := 16#3F# |

| U 2.5 altro digital (m). | |

| add_al_ana_u | add_t := 16#40# |

| U 2.5 altro analog (m). | |

| add_t4_th | add_t := 16#41# |

| Forth ADC T. | |

| add_va_rec_up_th | add_t := 16#42# |

| U 2.5 VA (m). | |

| add_va_sup_up_th | add_t := 16#43# |

| U 1.5 VA (m). | |

| add_va_sup_um_th | add_t := 16#44# |

| U -2.0 VA (m). | |

| add_va_rec_um_th | add_t := 16#45# |

| U -2.0 (m). | |

| add_t4 | add_t := 16#46# |

| Forth ADC T. | |

| add_va_rec_up | add_t := 16#47# |

| U 2.5 VA (m). | |

| add_va_sup_up | add_t := 16#48# |

| U 1.5 VA (m). | |

| add_va_sup_um | add_t := 16#49# |

| U -2.0 VA (m). | |

| add_va_rec_um | add_t := 16#4A# |

| U -2.0 (m). | |

| add_l1cnt | add_t := 16#0B# |

| L1 trigger CouNTer. | |

| add_l2cnt | add_t := 16#0C# |

| L2 trigger CouNTer. | |

| add_sclkcnt | add_t := 16#0D# |

| Sampling CLK CouNTer. | |

| add_dstbcnt | add_t := 16#0E# |

| DSTB CouNTer. | |

| add_tsm_word | add_t := 16#0F# |

| Test mode word. | |

| add_us_ratio | add_t := 16#10# |

| Undersampling ratio. | |

| add_csr0 | add_t := 16#11# |

| Config/Status Register 0. | |

| add_csr1 | add_t := 16#12# |

| Config/Status Register 1. | |

| add_csr2 | add_t := 16#13# |

| Config/Status Register 2. | |

| add_csr3 | add_t := 16#14# |

| Config/Status Register 3. | |

| add_free | add_t := 16#15# |

| Free. | |

| add_cntlat | add_t := 16#16# |

| Latch L1, L2, SCLK Counters. | |

| add_cntclr | add_t := 16#17# |

| Clear counters. | |

| add_csr1clr | add_t := 16#18# |

| Clear CSR1. | |

| add_alrst | add_t := 16#19# |

| rstb ALTROs | |

| add_bcrst | add_t := 16#1A# |

| rstb BC | |

| add_stcnv | add_t := 16#1B# |

| Start conversion. | |

| add_scevl | add_t := 16#1C# |

| Scan event length. | |

| add_evlrdo | add_t := 16#1D# |

| Read event length. | |

| add_sttsm | add_t := 16#1E# |

| Start test mode. | |

| add_acqrdo | add_t := 16#1F# |

| Read acquisition memory. | |

| add_fmdd_stat | add_t := 16#20# |

| FMDD status. | |

| add_l0cnt | add_t := 16#21# |

| L0 counters. | |

| add_hold_wait | add_t := 16#22# |

| FMD: Wait to hold. | |

| add_l1_timeout | add_t := 16#23# |

| FMD: L1 timeout. | |

| add_l2_timeout | add_t := 16#24# |

| FMD: L2 timeout. | |

| add_shift_div | add_t := 16#25# |

| FMD: Shift clk. | |

| add_strips | add_t := 16#26# |

| FMD: Strips. | |

| add_cal_level | add_t := 16#27# |

| FMD: Cal pulse. | |

| add_shape_bias | add_t := 16#28# |

| FMD: Shape bias. | |

| add_vfs | add_t := 16#29# |

| FMD: Shape ref. | |

| add_vfp | add_t := 16#2A# |

| FMD: Preamp ref. | |

| add_sample_div | add_t := 16#2B# |

| FMD: Sample clk. | |

| add_fmdd_cmd | add_t := 16#2C# |

| FMD: Commands. | |

| add_cal_iter | add_t := 16#4B# |

| FMD: Cal events. | |

| add_mebs | add_t := 16#4C# |

| Multi-event count/config. | |

| add_cal_delay | add_t := 16#4D# |

| Multi-event count/config. | |

| MAX_REG | integer := add_cal_delay |

| add_al_rpinc | std_logic_vector ( 4 downto 0 ) := " 11001 " |

| regs | regs_t := ( add_zero = > ( true , true , true , X " 0000 " ) , add_t1_th = > ( true , true , true , X " 00AF " ) , add_flash_i_th = > ( true , true , true , X " 0027 " ) , add_al_dig_i_th = > ( true , true , true , X " 004e " ) , add_al_ana_i_th = > ( true , true , true , X " 0045 " ) , add_va_rec_ip_th = > ( true , true , true , X " 0075 " ) , add_t1 = > ( false , true , false , X " 00AA " ) , add_flash_i = > ( false , true , false , X " 0027 " ) , add_al_dig_i = > ( false , true , false , X " 004e " ) , add_al_ana_i = > ( false , true , false , X " 0045 " ) , add_va_rec_ip = > ( false , true , false , X " 0075 " ) , add_t2_th = > ( true , true , true , X " 00AF " ) , add_va_sup_ip_th = > ( true , true , true , X " 0089 " ) , add_va_rec_im_th = > ( true , true , true , X " 00a6 " ) , add_va_sup_im_th = > ( true , true , true , X " 0186 " ) , add_gtl_u_th = > ( true , true , true , X " 01d6 " ) , add_t2 = > ( false , true , false , X " 00AA " ) , add_va_sup_ip = > ( false , true , false , X " 0089 " ) , add_va_rec_im = > ( false , true , false , X " 00a6 " ) , add_va_sup_im = > ( false , true , false , X " 0186 " ) , add_gtl_u = > ( false , true , false , X " 01d6 " ) , add_t3_th = > ( true , true , true , X " 00AF " ) , add_t1sens_th = > ( true , true , true , X " 01cf " ) , add_t2sens_th = > ( true , true , true , X " 01cf " ) , add_al_dig_u_th = > ( true , true , true , X " 01d6 " ) , add_al_ana_u_th = > ( true , true , true , X " 01d6 " ) , add_t3 = > ( false , true , false , X " 00Aa " ) , add_t1sens = > ( false , true , false , X " 01bf " ) , add_t2sens = > ( false , true , false , X " 01bf " ) , add_al_dig_u = > ( false , true , false , X " 01d6 " ) , add_al_ana_u = > ( false , true , false , X " 01d6 " ) , add_t4_th = > ( true , true , true , X " 00AF " ) , add_va_rec_up_th = > ( true , true , true , X " 01d6 " ) , add_va_sup_up_th = > ( true , true , true , X " 0109 " ) , add_va_sup_um_th = > ( true , true , true , X " 008F " ) , add_va_rec_um_th = > ( true , true , true , X " 008F " ) , add_t4 = > ( false , true , false , X " 00AA " ) , add_va_rec_up = > ( false , true , false , X " 01d6 " ) , add_va_sup_up = > ( false , true , false , X " 0109 " ) , add_va_sup_um = > ( false , true , false , X " 008F " ) , add_va_rec_um = > ( false , true , false , X " 008F " ) , add_l1cnt = > ( false , true , false , X " 0000 " ) , add_l2cnt = > ( false , true , false , X " 0000 " ) , add_sclkcnt = > ( false , false , false , X " 0000 " ) , add_dstbcnt = > ( false , false , false , X " 0000 " ) , add_tsm_word = > ( true , false , true , X " 0001 " ) , add_us_ratio = > ( true , false , true , X " 0001 " ) , add_csr0 = > ( true , true , true , X " 07F9 " ) , add_csr1 = > ( true , true , true , X " 0000 " ) , add_csr2 = > ( true , true , true , X " 000F " ) , add_csr3 = > ( true , true , true , X " 2220 " ) , add_free = > ( false , true , false , version ) , add_cntlat = > ( true , true , true , X " 0000 " ) , add_cntclr = > ( true , true , true , X " 0000 " ) , add_csr1clr = > ( true , true , true , X " 0000 " ) , add_alrst = > ( true , true , true , X " 0000 " ) , add_bcrst = > ( true , true , true , X " 0000 " ) , add_stcnv = > ( true , true , true , X " 0000 " ) , add_scevl = > ( true , false , true , X " 0000 " ) , add_evlrdo = > ( true , false , true , X " 0000 " ) , add_sttsm = > ( true , false , true , X " 0000 " ) , add_acqrdo = > ( true , false , true , X " 0000 " ) , add_fmdd_stat = > ( true , false , false , X " 0000 " ) , add_l0cnt = > ( true , true , false , X " 0000 " ) , add_hold_wait = > ( true , false , true , X " 0020 " ) , add_l1_timeout = > ( true , false , true , X " 00F0 " ) , add_l2_timeout = > ( true , false , true , X " 0E00 " ) , add_shift_div = > ( true , false , true , X " 1000 " ) , add_strips = > ( true , false , true , X " 7F00 " ) , add_cal_level = > ( true , false , true , X " 2000 " ) , add_shape_bias = > ( true , false , true , X " 2A20 " ) , add_vfs = > ( true , false , true , X " 645D " ) , add_vfp = > ( true , false , true , X " 878B " ) , add_sample_div = > ( true , false , true , X " 0402 " ) , add_fmdd_cmd = > ( true , false , true , X " 0000 " ) , add_cal_iter = > ( true , false , true , X " 0064 " ) , add_mebs = > ( true , false , true , X " 0144 " ) , add_cal_delay = > ( true , false , true , X " 0030 " ) , others = > ( false , false , false , X " 0000 " ) ) |

| BASE_ADC | integer := 6 |

| Base address for ADCs. | |

| NUM_ADC | integer := 20 |

| number of ADC's | |

| adc_map | adc_map_t := ( add_t1 , add_flash_i , add_al_dig_i , add_al_ana_i , add_va_rec_ip , add_t2 , add_va_sup_ip , add_va_rec_im , add_va_sup_im , add_gtl_u , add_t3 , add_t1sens , add_t2sens , add_al_dig_u , add_al_ana_u , add_t4 , add_va_rec_up , add_va_sup_up , add_va_sup_um , add_va_rec_um ) |

| adc_rmap | adc_rmap_t := ( add_t1 = > BASE_ADC , add_flash_i = > BASE_ADC +1 , add_al_dig_i = > BASE_ADC +2 , add_al_ana_i = > BASE_ADC +3 , add_va_rec_ip = > BASE_ADC +4 , add_t2 = > BASE_ADC +5 , add_va_sup_ip = > BASE_ADC +6 , add_va_rec_im = > BASE_ADC +7 , add_va_sup_im = > BASE_ADC +8 , add_gtl_u = > BASE_ADC +9 , add_t3 = > BASE_ADC +10 , add_t1sens = > BASE_ADC +11 , add_t2sens = > BASE_ADC +12 , add_al_dig_u = > BASE_ADC +13 , add_al_ana_u = > BASE_ADC +14 , add_t4 = > BASE_ADC +15 , add_va_rec_up = > BASE_ADC +16 , add_va_sup_up = > BASE_ADC +17 , add_va_sup_um = > BASE_ADC +18 , add_va_rec_um = > BASE_ADC +19 , others = > 0 ) |

Types | |

| regs_t | array ( MAX_REG downto 0 ) of reg_t |

| adc_map_t | array ( BASE_ADC to NUM_ADC +BASE_ADC -1 ) of integer range 0 to 2 **7-1 |

| adc_rmap_t | array ( 0 to add_va_rec_um ) of integer range 0 to NUM_ADC +BASE_ADC -1 |

| Map type. | |

Subtypes | |

| add_t | integer range 0 to NUM_REG |

| Address type. | |

| regval_t | std_logic_vector ( 15 downto 0 ) |

| Register value. | |

Records | |

| reg_t : record | |

| bcast | boolean |

| Allow broadcast. | |

| sc | boolean |

| Allow slow control. | |

| w | boolean |

| Allow write. | |

| def | regval_t |

| Default value. | |

Detailed Description

This package holds the configruation for the registers of the board controller.

Member Data Documentation

bcast boolean [Record] |

Allow broadcast.

Record describing registers

sc boolean [Record] |

Allow slow control.

w boolean [Record] |

Allow write.

adc_map adc_map_t := ( add_t1 , add_flash_i , add_al_dig_i , add_al_ana_i , add_va_rec_ip , add_t2 , add_va_sup_ip , add_va_rec_im , add_va_sup_im , add_gtl_u , add_t3 , add_t1sens , add_t2sens , add_al_dig_u , add_al_ana_u , add_t4 , add_va_rec_up , add_va_sup_up , add_va_sup_um , add_va_rec_um ) [Constant] |

adc_rmap adc_rmap_t := ( add_t1 = > BASE_ADC , add_flash_i = > BASE_ADC +1 , add_al_dig_i = > BASE_ADC +2 , add_al_ana_i = > BASE_ADC +3 , add_va_rec_ip = > BASE_ADC +4 , add_t2 = > BASE_ADC +5 , add_va_sup_ip = > BASE_ADC +6 , add_va_rec_im = > BASE_ADC +7 , add_va_sup_im = > BASE_ADC +8 , add_gtl_u = > BASE_ADC +9 , add_t3 = > BASE_ADC +10 , add_t1sens = > BASE_ADC +11 , add_t2sens = > BASE_ADC +12 , add_al_dig_u = > BASE_ADC +13 , add_al_ana_u = > BASE_ADC +14 , add_t4 = > BASE_ADC +15 , add_va_rec_up = > BASE_ADC +16 , add_va_sup_up = > BASE_ADC +17 , add_va_sup_um = > BASE_ADC +18 , add_va_rec_um = > BASE_ADC +19 , others = > 0 ) [Constant] |

adc_rmap_t array ( 0 to add_va_rec_um ) of integer range 0 to NUM_ADC +BASE_ADC -1 [Type] |

Map type.

add_acqrdo add_t := 16#1F# [Constant] |

Read acquisition memory.

add_al_ana_i add_t := 16#09# [Constant] |

I 2.5 V altro analog.

add_al_ana_i_th add_t := 16#04# [Constant] |

I 2.5 V altro analog.

add_al_ana_u add_t := 16#40# [Constant] |

U 2.5 altro analog (m).

add_al_ana_u_th add_t := 16#3B# [Constant] |

U 2.5 altro analog (m).

add_al_dig_i add_t := 16#08# [Constant] |

I 2.5 V altro digital.

add_al_dig_i_th add_t := 16#03# [Constant] |

I 2.5 V altro digital.

add_al_dig_u add_t := 16#3F# [Constant] |

U 2.5 altro digital (m).

add_al_dig_u_th add_t := 16#3A# [Constant] |

U 2.5 altro digital (m).

add_al_rpinc std_logic_vector ( 4 downto 0 ) := " 11001 " [Constant] |

ADD_BITS integer := 7 [Constant] |

Number of addrss bits.

add_cal_delay add_t := 16#4D# [Constant] |

Multi-event count/config.

add_cal_iter add_t := 16#4B# [Constant] |

FMD: Cal events.

add_cal_level add_t := 16#27# [Constant] |

FMD: Cal pulse.

add_cntclr add_t := 16#17# [Constant] |

Clear counters.

add_cntlat add_t := 16#16# [Constant] |

Latch L1, L2, SCLK Counters.

add_csr1clr add_t := 16#18# [Constant] |

Clear CSR1.

add_dstbcnt add_t := 16#0E# [Constant] |

DSTB CouNTer.

add_evlrdo add_t := 16#1D# [Constant] |

Read event length.

add_flash_i add_t := 16#07# [Constant] |

I 3.3 V.

add_flash_i_th add_t := 16#02# [Constant] |

I 3.3 V.

add_fmdd_cmd add_t := 16#2C# [Constant] |

FMD: Commands.

add_fmdd_stat add_t := 16#20# [Constant] |

FMDD status.

add_gtl_u_th add_t := 16#31# [Constant] |

2.5 V Digital driver

add_hold_wait add_t := 16#22# [Constant] |

FMD: Wait to hold.

add_l1_timeout add_t := 16#23# [Constant] |

FMD: L1 timeout.

add_l2_timeout add_t := 16#24# [Constant] |

FMD: L2 timeout.

add_sample_div add_t := 16#2B# [Constant] |

FMD: Sample clk.

add_sclkcnt add_t := 16#0D# [Constant] |

Sampling CLK CouNTer.

add_shape_bias add_t := 16#28# [Constant] |

FMD: Shape bias.

add_shift_div add_t := 16#25# [Constant] |

FMD: Shift clk.

add_strips add_t := 16#26# [Constant] |

FMD: Strips.

add_t1sens add_t := 16#3D# [Constant] |

Temperature sens. 1.

add_t1sens_th add_t := 16#38# [Constant] |

Temperature sens. 1.

add_t2sens add_t := 16#3E# [Constant] |

Temperature sens. 2.

add_t2sens_th add_t := 16#39# [Constant] |

Temperature sens. 2.

add_tsm_word add_t := 16#0F# [Constant] |

Test mode word.

add_us_ratio add_t := 16#10# [Constant] |

Undersampling ratio.

add_va_rec_im add_t := 16#34# [Constant] |

I -2.0 V.

add_va_rec_im_th add_t := 16#2F# [Constant] |

I -2.0 V.

add_va_rec_ip add_t := 16#0A# [Constant] |

I 2.5 V VA.

add_va_rec_ip_th add_t := 16#05# [Constant] |

I 2.5 V VA.

add_va_rec_um add_t := 16#4A# [Constant] |

U -2.0 (m).

add_va_rec_um_th add_t := 16#45# [Constant] |

U -2.0 (m).

add_va_rec_up add_t := 16#47# [Constant] |

U 2.5 VA (m).

add_va_rec_up_th add_t := 16#42# [Constant] |

U 2.5 VA (m).

add_va_sup_im add_t := 16#35# [Constant] |

I -2.0 V VA.

add_va_sup_im_th add_t := 16#30# [Constant] |

I -2.0 V VA.

add_va_sup_ip add_t := 16#33# [Constant] |

I 1.5 V VA.

add_va_sup_ip_th add_t := 16#2E# [Constant] |

I 1.5 V VA.

add_va_sup_um add_t := 16#49# [Constant] |

U -2.0 VA (m).

add_va_sup_um_th add_t := 16#44# [Constant] |

U -2.0 VA (m).

add_va_sup_up add_t := 16#48# [Constant] |

U 1.5 VA (m).

add_va_sup_up_th add_t := 16#43# [Constant] |

U 1.5 VA (m).

BASE_ADC integer := 6 [Constant] |

Base address for ADCs.

ieee library [Library] |

MAX_REG integer := add_cal_delay [Constant] |

NUM_ADC integer := 20 [Constant] |

number of ADC's

numeric_std package [Package] |

reg_t [Record] |

regs regs_t := ( add_zero = > ( true , true , true , X " 0000 " ) , add_t1_th = > ( true , true , true , X " 00AF " ) , add_flash_i_th = > ( true , true , true , X " 0027 " ) , add_al_dig_i_th = > ( true , true , true , X " 004e " ) , add_al_ana_i_th = > ( true , true , true , X " 0045 " ) , add_va_rec_ip_th = > ( true , true , true , X " 0075 " ) , add_t1 = > ( false , true , false , X " 00AA " ) , add_flash_i = > ( false , true , false , X " 0027 " ) , add_al_dig_i = > ( false , true , false , X " 004e " ) , add_al_ana_i = > ( false , true , false , X " 0045 " ) , add_va_rec_ip = > ( false , true , false , X " 0075 " ) , add_t2_th = > ( true , true , true , X " 00AF " ) , add_va_sup_ip_th = > ( true , true , true , X " 0089 " ) , add_va_rec_im_th = > ( true , true , true , X " 00a6 " ) , add_va_sup_im_th = > ( true , true , true , X " 0186 " ) , add_gtl_u_th = > ( true , true , true , X " 01d6 " ) , add_t2 = > ( false , true , false , X " 00AA " ) , add_va_sup_ip = > ( false , true , false , X " 0089 " ) , add_va_rec_im = > ( false , true , false , X " 00a6 " ) , add_va_sup_im = > ( false , true , false , X " 0186 " ) , add_gtl_u = > ( false , true , false , X " 01d6 " ) , add_t3_th = > ( true , true , true , X " 00AF " ) , add_t1sens_th = > ( true , true , true , X " 01cf " ) , add_t2sens_th = > ( true , true , true , X " 01cf " ) , add_al_dig_u_th = > ( true , true , true , X " 01d6 " ) , add_al_ana_u_th = > ( true , true , true , X " 01d6 " ) , add_t3 = > ( false , true , false , X " 00Aa " ) , add_t1sens = > ( false , true , false , X " 01bf " ) , add_t2sens = > ( false , true , false , X " 01bf " ) , add_al_dig_u = > ( false , true , false , X " 01d6 " ) , add_al_ana_u = > ( false , true , false , X " 01d6 " ) , add_t4_th = > ( true , true , true , X " 00AF " ) , add_va_rec_up_th = > ( true , true , true , X " 01d6 " ) , add_va_sup_up_th = > ( true , true , true , X " 0109 " ) , add_va_sup_um_th = > ( true , true , true , X " 008F " ) , add_va_rec_um_th = > ( true , true , true , X " 008F " ) , add_t4 = > ( false , true , false , X " 00AA " ) , add_va_rec_up = > ( false , true , false , X " 01d6 " ) , add_va_sup_up = > ( false , true , false , X " 0109 " ) , add_va_sup_um = > ( false , true , false , X " 008F " ) , add_va_rec_um = > ( false , true , false , X " 008F " ) , add_l1cnt = > ( false , true , false , X " 0000 " ) , add_l2cnt = > ( false , true , false , X " 0000 " ) , add_sclkcnt = > ( false , false , false , X " 0000 " ) , add_dstbcnt = > ( false , false , false , X " 0000 " ) , add_tsm_word = > ( true , false , true , X " 0001 " ) , add_us_ratio = > ( true , false , true , X " 0001 " ) , add_csr0 = > ( true , true , true , X " 07F9 " ) , add_csr1 = > ( true , true , true , X " 0000 " ) , add_csr2 = > ( true , true , true , X " 000F " ) , add_csr3 = > ( true , true , true , X " 2220 " ) , add_free = > ( false , true , false , version ) , add_cntlat = > ( true , true , true , X " 0000 " ) , add_cntclr = > ( true , true , true , X " 0000 " ) , add_csr1clr = > ( true , true , true , X " 0000 " ) , add_alrst = > ( true , true , true , X " 0000 " ) , add_bcrst = > ( true , true , true , X " 0000 " ) , add_stcnv = > ( true , true , true , X " 0000 " ) , add_scevl = > ( true , false , true , X " 0000 " ) , add_evlrdo = > ( true , false , true , X " 0000 " ) , add_sttsm = > ( true , false , true , X " 0000 " ) , add_acqrdo = > ( true , false , true , X " 0000 " ) , add_fmdd_stat = > ( true , false , false , X " 0000 " ) , add_l0cnt = > ( true , true , false , X " 0000 " ) , add_hold_wait = > ( true , false , true , X " 0020 " ) , add_l1_timeout = > ( true , false , true , X " 00F0 " ) , add_l2_timeout = > ( true , false , true , X " 0E00 " ) , add_shift_div = > ( true , false , true , X " 1000 " ) , add_strips = > ( true , false , true , X " 7F00 " ) , add_cal_level = > ( true , false , true , X " 2000 " ) , add_shape_bias = > ( true , false , true , X " 2A20 " ) , add_vfs = > ( true , false , true , X " 645D " ) , add_vfp = > ( true , false , true , X " 878B " ) , add_sample_div = > ( true , false , true , X " 0402 " ) , add_fmdd_cmd = > ( true , false , true , X " 0000 " ) , add_cal_iter = > ( true , false , true , X " 0064 " ) , add_mebs = > ( true , false , true , X " 0144 " ) , add_cal_delay = > ( true , false , true , X " 0030 " ) , others = > ( false , false , false , X " 0000 " ) ) [Constant] |

regval_t std_logic_vector ( 15 downto 0 ) [Subtype] |

Register value.

std_logic_1164 package [Package] |

version std_logic_vector ( 15 downto 0 ) := X " 0220 " [Constant] |

Version number X"0113" -> Major: 0x01, minor: 0x13=19 Version number.

The documentation for this class was generated from the following file:

1.6.2-20100208

1.6.2-20100208