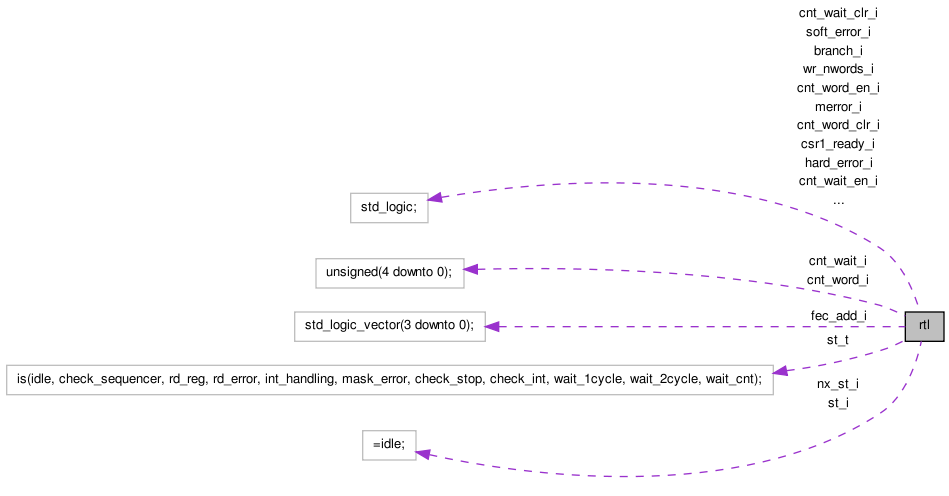

rtl Architecture Reference

List of all members.

Processes |

| next_state | ( clk , rstb ) |

| fsm | ( st_i , interrupt , seq_active , stop , csr1 , hard_error_i , master_end , error , last_card , cnt_wait_i ) |

| output_addresses | ( clk , rstb ) |

| word_counter | ( clk , rstb ) |

| validated_fecs | ( clk , rstb ) |

| address_status | ( clk , rstb ) |

| wait_counter | ( clk , rstb ) |

Types |

| st_t | ( idle , check_sequencer , rd_reg , rd_error , int_handling , mask_error , check_stop , check_int , wait_1cycle , wait_2cycle , wait_cnt ) |

Signals |

| branch_i | |

| fec_add_i | ( 3 downto 0 ) |

| st_i | st_t := idle |

| nx_st_i | st_t := idle |

| hard_error_i | |

| soft_error_i | |

| csr1_ready_i | |

| merror_i | |

| wr_nwords_i | |

| cnt_wait_clr_i | |

| cnt_wait_en_i | |

| cnt_wait_i | ( 4 downto 0 ) |

| cnt_word_clr_i | |

| cnt_word_en_i | |

| cnt_word_i | ( 4 downto 0 ) |

Member Function Documentation

| address_status | |

( clk , |

|

|

rstb ) |

[Process]

| fsm | |

( st_i , |

|

|

interrupt , |

|

|

seq_active , |

|

|

stop , |

|

|

csr1 , |

|

|

hard_error_i , |

|

|

master_end , |

|

|

error , |

|

|

last_card , |

|

|

cnt_wait_i ) |

[Process]

| next_state | |

( clk , |

|

|

rstb ) |

[Process]

| output_addresses | |

( clk , |

|

|

rstb ) |

[Process]

| validated_fecs | |

( clk , |

|

|

rstb ) |

[Process]

| wait_counter | |

( clk , |

|

|

rstb ) |

[Process]

| word_counter | |

( clk , |

|

|

rstb ) |

[Process]

Member Data Documentation

st_t ( idle , check_sequencer , rd_reg , rd_error , int_handling , mask_error , check_stop , check_int , wait_1cycle , wait_2cycle , wait_cnt ) [Type] |

The documentation for this class was generated from the following file:

1.6.2-20100208

1.6.2-20100208