rtl Architecture Reference

Inheritance diagram for rtl:

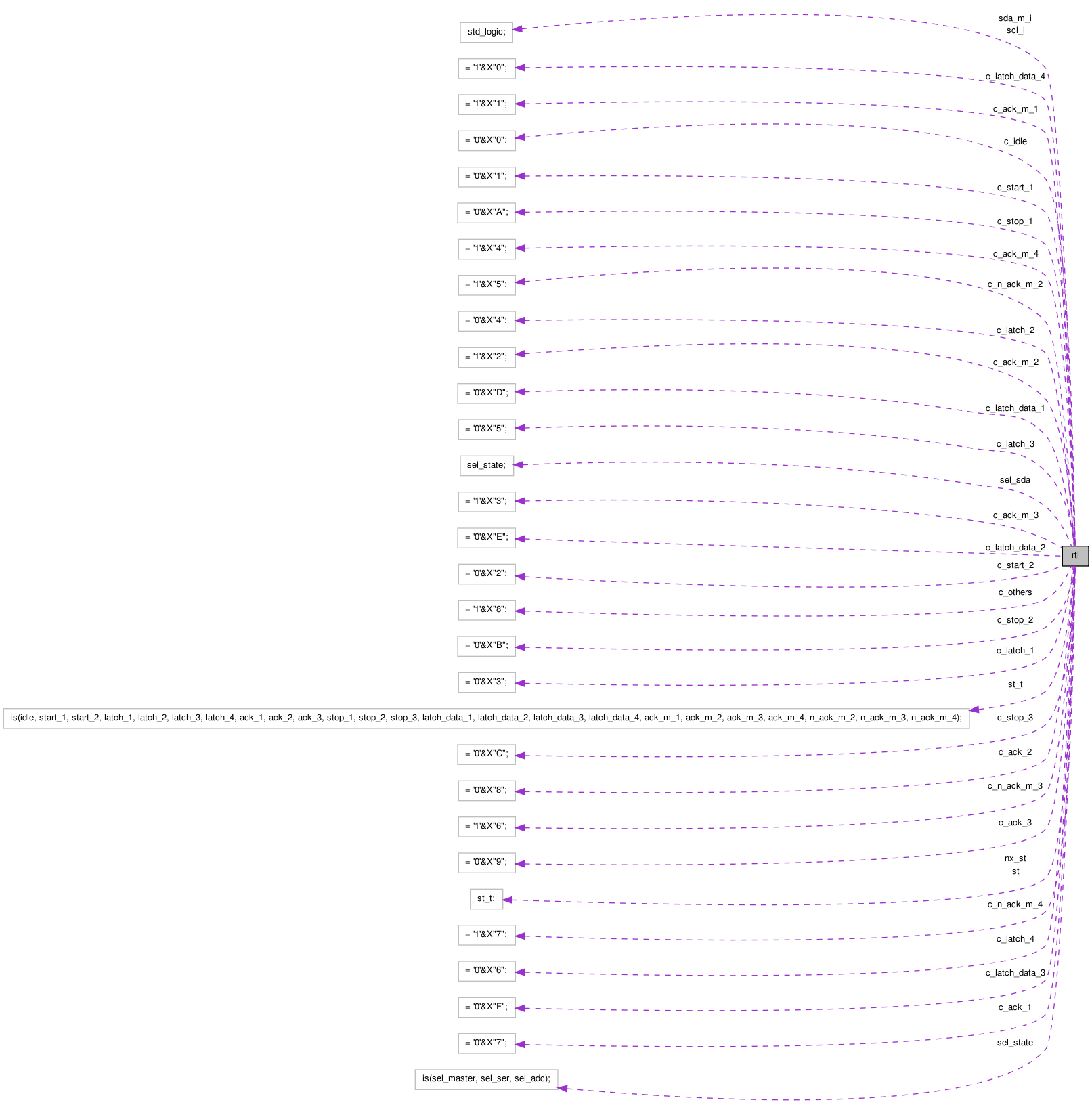

Collaboration diagram for rtl:

Processes | |

| update_state | ( clk , rstb ) |

| fsm | ( st , start , stop , cnt_8 , rw , width , new_data , cnt_2 , sda ) |

| select_inout | ( clk , rstb ) |

Constants | |

| c_idle | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 0 " |

| c_start_1 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 1 " |

| c_start_2 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 2 " |

| c_latch_1 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 3 " |

| c_latch_2 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 4 " |

| c_latch_3 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 5 " |

| c_latch_4 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 6 " |

| c_ack_1 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 7 " |

| c_ack_2 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 8 " |

| c_ack_3 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 9 " |

| c_stop_1 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " A " |

| c_stop_2 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " B " |

| c_stop_3 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " C " |

| c_latch_data_1 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " D " |

| c_latch_data_2 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " E " |

| c_latch_data_3 | std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " F " |

| c_latch_data_4 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 0 " |

| c_ack_m_1 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 1 " |

| c_ack_m_2 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 2 " |

| c_ack_m_3 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 3 " |

| c_ack_m_4 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 4 " |

| c_n_ack_m_2 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 5 " |

| c_n_ack_m_3 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 6 " |

| c_n_ack_m_4 | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 7 " |

| c_others | std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 8 " |

Types | |

| st_t | ( idle , start_1 , start_2 , latch_1 , latch_2 , latch_3 , latch_4 , ack_1 , ack_2 , ack_3 , stop_1 , stop_2 , stop_3 , latch_data_1 , latch_data_2 , latch_data_3 , latch_data_4 , ack_m_1 , ack_m_2 , ack_m_3 , ack_m_4 , n_ack_m_2 , n_ack_m_3 , n_ack_m_4 ) |

| sel_state | ( sel_master , sel_ser , sel_adc ) |

Signals | |

| st | st_t |

| nx_st | st_t |

| sel_sda | sel_state |

| scl_i | std_logic |

| sda_m_i | std_logic |

Member Function Documentation

| fsm | ( st , | |

| start , | ||

| stop , | ||

| cnt_8 , | ||

| rw , | ||

| width , | ||

| new_data , | ||

| cnt_2 , | ||

| sda ) |

| select_inout | ( clk , | |

| rstb ) |

| update_state | ( clk , | |

| rstb ) |

Member Data Documentation

c_ack_1 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 7 " [Constant] |

c_ack_2 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 8 " [Constant] |

c_ack_3 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 9 " [Constant] |

c_ack_m_1 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 1 " [Constant] |

c_ack_m_2 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 2 " [Constant] |

c_ack_m_3 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 3 " [Constant] |

c_ack_m_4 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 4 " [Constant] |

c_idle std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 0 " [Constant] |

c_latch_1 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 3 " [Constant] |

c_latch_2 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 4 " [Constant] |

c_latch_3 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 5 " [Constant] |

c_latch_4 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 6 " [Constant] |

c_latch_data_1 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " D " [Constant] |

c_latch_data_2 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " E " [Constant] |

c_latch_data_3 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " F " [Constant] |

c_latch_data_4 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 0 " [Constant] |

c_n_ack_m_2 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 5 " [Constant] |

c_n_ack_m_3 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 6 " [Constant] |

c_n_ack_m_4 std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 7 " [Constant] |

c_others std_logic_vector ( 4 downto 0 ) := ' 1 ' &X " 8 " [Constant] |

c_start_1 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 1 " [Constant] |

c_start_2 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " 2 " [Constant] |

c_stop_1 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " A " [Constant] |

c_stop_2 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " B " [Constant] |

c_stop_3 std_logic_vector ( 4 downto 0 ) := ' 0 ' &X " C " [Constant] |

scl_i std_logic [Signal] |

sda_m_i std_logic [Signal] |

sel_state ( sel_master , sel_ser , sel_adc ) [Type] |

st_t ( idle , start_1 , start_2 , latch_1 , latch_2 , latch_3 , latch_4 , ack_1 , ack_2 , ack_3 , stop_1 , stop_2 , stop_3 , latch_data_1 , latch_data_2 , latch_data_3 , latch_data_4 , ack_m_1 , ack_m_2 , ack_m_3 , ack_m_4 , n_ack_m_2 , n_ack_m_3 , n_ack_m_4 ) [Type] |

The documentation for this class was generated from the following file:

- bc/bc_core/interface_adc/master/master_sm/master_sm.vhd

1.6.2-20100208

1.6.2-20100208