intexec Entity Reference

[Model of ALTRO chip]

Inheritance diagram for intexec:

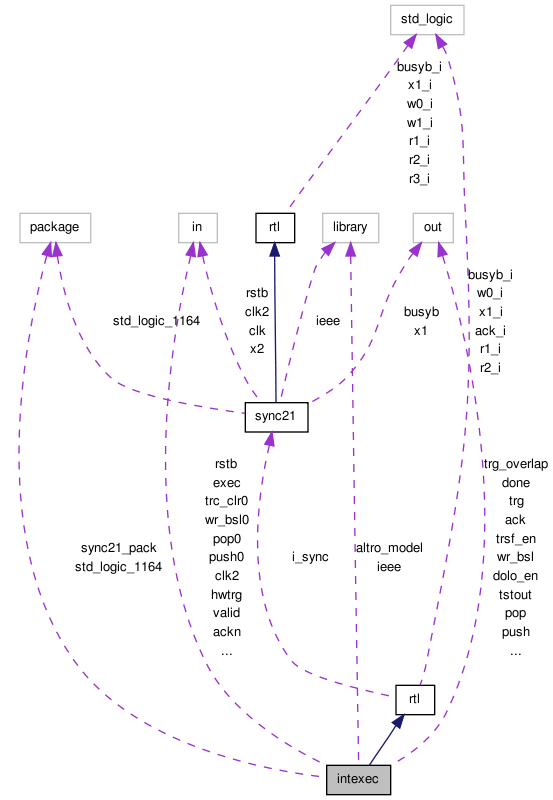

Collaboration diagram for intexec:

Architectures | |

| rtl | Architecture |

Libraries | |

| ieee | |

| altro_model | |

Packages | |

| std_logic_1164 | |

| sync21_pack | Package <sync21_pack> |

Ports | |

| l2y_r | in std_logic |

| L2 accept. | |

| exec | in std_logic |

| exec state | |

| en1 | in std_logic |

| en1 state | |

| ackn | in std_logic |

| acknowledge state | |

| en2 | in std_logic |

| en2 state | |

| waitst | in std_logic |

| Wait state. | |

| clk2 | in std_logic |

| Clock 2. | |

| rstb | in std_logic |

| reset | |

| clk | in std_logic |

| clock | |

| valid | in std_logic |

| valid data | |

| chrdo0 | in std_logic |

| channel r/o | |

| rg_rd0 | in std_logic |

| read register | |

| rg_wr0 | in std_logic |

| write register | |

| push0 | in std_logic |

| Push it. | |

| pop0 | in std_logic |

| Pop it. | |

| swtrg | in std_logic |

| software trigger | |

| trc_clr0 | in std_logic |

| trigger counter clear | |

| err_clr0 | in std_logic |

| error clear | |

| wr_bsl0 | in std_logic |

| write | |

| rd_bsl0 | in std_logic |

| read | |

| bcast | in std_logic |

| broadcast flag | |

| hwtrg | in std_logic |

| hardware trigger | |

| twx | in std_logic |

| Test mode. | |

| done | out std_logic |

| Done. | |

| ack | out std_logic |

| Acknowledge. | |

| ack_en | out std_logic |

| Enable acknowledge. | |

| dolo_en | out std_logic |

| Enable output. | |

| trsf_en | out std_logic |

| Enable transfer. | |

| trg_overlap | out std_logic |

| Trigger overlap. | |

| rg_wr | out std_logic |

| Register write. | |

| push | out std_logic |

| Push it. | |

| pop | out std_logic |

| Pop it. | |

| trg | out std_logic |

| Trigger. | |

| trc_clr | out std_logic |

| Clear trigger counter. | |

| err_clr | out std_logic |

| Error clear. | |

| wr_bsl | out std_logic |

| Write base line. | |

| rd_bsl | out std_logic |

| Read base line. | |

| tstout | out std_logic |

| Test mode out. | |

Detailed Description

Execute instructions

Member Data Documentation

ack out std_logic [Port] |

Acknowledge.

ack_en out std_logic [Port] |

Enable acknowledge.

ackn in std_logic [Port] |

acknowledge state

altro_model library [Library] |

bcast in std_logic [Port] |

broadcast flag

chrdo0 in std_logic [Port] |

channel r/o

clk in std_logic [Port] |

clock

clk2 in std_logic [Port] |

Clock 2.

dolo_en out std_logic [Port] |

Enable output.

done out std_logic [Port] |

Done.

en1 in std_logic [Port] |

en1 state

en2 in std_logic [Port] |

en2 state

err_clr out std_logic [Port] |

Error clear.

err_clr0 in std_logic [Port] |

error clear

exec in std_logic [Port] |

exec state

hwtrg in std_logic [Port] |

hardware trigger

ieee library [Library] |

l2y_r in std_logic [Port] |

L2 accept.

pop out std_logic [Port] |

Pop it.

pop0 in std_logic [Port] |

Pop it.

push out std_logic [Port] |

Push it.

push0 in std_logic [Port] |

Push it.

rd_bsl out std_logic [Port] |

Read base line.

rd_bsl0 in std_logic [Port] |

read

rg_rd0 in std_logic [Port] |

read register

rg_wr out std_logic [Port] |

Register write.

rg_wr0 in std_logic [Port] |

write register

rstb in std_logic [Port] |

reset

std_logic_1164 package [Package] |

swtrg in std_logic [Port] |

software trigger

sync21_pack package [Package] |

trc_clr out std_logic [Port] |

Clear trigger counter.

trc_clr0 in std_logic [Port] |

trigger counter clear

trg out std_logic [Port] |

Trigger.

trg_overlap out std_logic [Port] |

Trigger overlap.

trsf_en out std_logic [Port] |

Enable transfer.

tstout out std_logic [Port] |

Test mode out.

twx in std_logic [Port] |

Test mode.

valid in std_logic [Port] |

valid data

waitst in std_logic [Port] |

Wait state.

wr_bsl out std_logic [Port] |

Write base line.

wr_bsl0 in std_logic [Port] |

write

The documentation for this class was generated from the following file:

- altro/intexec.vhd

1.6.2-20100208

1.6.2-20100208