rtl Architecture Reference

Inheritance diagram for rtl:

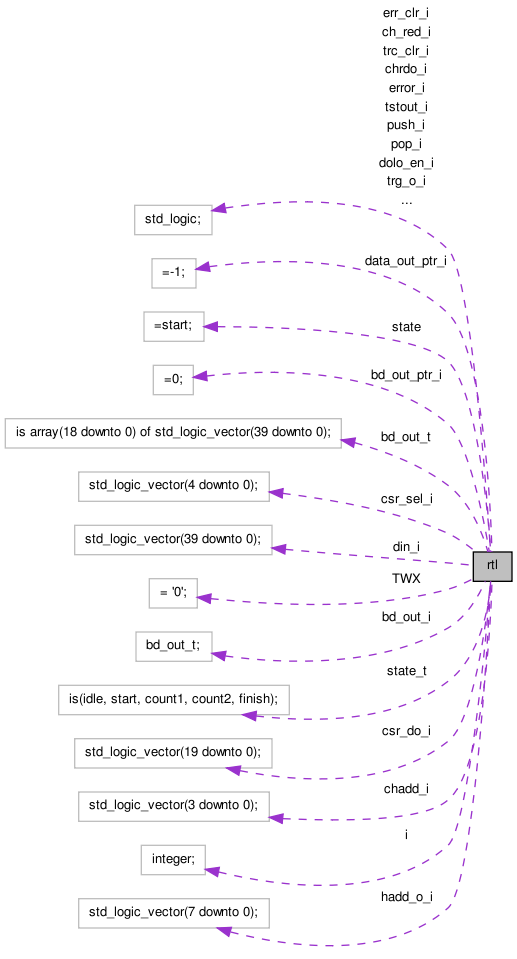

Collaboration diagram for rtl:

Functions | |

| std_logic_vector | conv_std_logic_vector ( constant x: in integer , constant n: in natural ) |

Processes | |

| PROCESS_1 | ( chrdo_i , clk2 , rstb ) |

| PROCESS_2 | ( mixerror_i , err_clr_i , rstb ) |

Constants | |

| TWX | std_logic := ' 0 ' |

Types | |

| state_t | ( idle , start , count1 , count2 , finish ) |

| state type | |

| bd_out_t | array ( 18 downto 0 ) of std_logic_vector ( 39 downto 0 ) |

Signals | |

| ch_red_i | std_logic |

| din_i | std_logic_vector ( 39 downto 0 ) |

| Data input. | |

| write_i | std_logic |

| write | |

| h_abt_i | std_logic |

| Hamming encoding. | |

| h_err_i | std_logic |

| Hamming encoding error. | |

| chrdo_i | std_logic |

| channel read-out | |

| ack_i | std_logic |

| Acknowledge. | |

| ack_en_i | std_logic |

| Enable acknowledge. | |

| dolo_en_i | std_logic |

| Data output enable. | |

| trsf_i | std_logic |

| Transfer gate. | |

| trsf_en_i | std_logic |

| Enable transfer. | |

| trg_overlap_i | std_logic |

| Trigger overlap. | |

| csr_wr_i | std_logic |

| Config/status write. | |

| pop_i | std_logic |

| Pop an event. | |

| push_i | std_logic |

| Push an event. | |

| trg_o_i | std_logic |

| Trigger. | |

| trc_clr_i | std_logic |

| Clear trigger. | |

| err_clr_i | std_logic |

| Error clear. | |

| wr_bsl_i | std_logic |

| Write baseline. | |

| rd_bsl_i | std_logic |

| Read baseline. | |

| instr_err_i | std_logic |

| Instruction error. | |

| bcast_i | std_logic |

| Broadcast. | |

| chadd_i | std_logic_vector ( 3 downto 0 ) |

| Channel address. | |

| csr_sel_i | std_logic_vector ( 4 downto 0 ) |

| CSR select. | |

| hadd_o_i | std_logic_vector ( 7 downto 0 ) |

| HW address. | |

| csr_do_i | std_logic_vector ( 19 downto 0 ) |

| CSR do. | |

| par_err_i | std_logic |

| Parity error. | |

| tstout_i | std_logic |

| Test out. | |

| mixerror_i | std_logic |

| Mixed error. | |

| error_i | std_logic |

| Error. | |

| i | integer |

| Counter. | |

| cst_i | std_logic |

| Control strobe. | |

| state | state_t := start |

| state | |

| bd_out_i | bd_out_t |

| Data out. | |

| bd_out_ptr_i | integer := 0 |

| Pointer into data out. | |

| data_out_ptr_i | integer := -1 |

| Data out pointer. | |

Member Function Documentation

| std_logic_vector conv_std_logic_vector | (constant x in integer , | |

| constant n in natural ) |

Convert integer to std_logic_vector

- Parameters:

-

x Integer to convert n Size (in bits) of integer

| PROCESS_1 | ( chrdo_i , | |

| clk2 , | ||

| rstb ) |

State machine to control delayed response

- Parameters:

-

chrdo_i Channel readout clk2 Slow clock rstb Asyncronous reset

| PROCESS_2 | ( mixerror_i , | |

| err_clr_i , | ||

| rstb ) |

Error outout

- Parameters:

-

mixerror_i Mixed error err_clr_i Clear errors rstb Async reset

Member Data Documentation

ack_en_i std_logic [Signal] |

Enable acknowledge.

ack_i std_logic [Signal] |

Acknowledge.

bcast_i std_logic [Signal] |

Broadcast.

bd_out_ptr_i integer := 0 [Signal] |

Pointer into data out.

bd_out_t array ( 18 downto 0 ) of std_logic_vector ( 39 downto 0 ) [Type] |

ch_red_i std_logic [Signal] |

chadd_i std_logic_vector ( 3 downto 0 ) [Signal] |

Channel address.

chrdo_i std_logic [Signal] |

channel read-out

csr_do_i std_logic_vector ( 19 downto 0 ) [Signal] |

CSR do.

csr_sel_i std_logic_vector ( 4 downto 0 ) [Signal] |

CSR select.

csr_wr_i std_logic [Signal] |

Config/status write.

cst_i std_logic [Signal] |

Control strobe.

data_out_ptr_i integer := -1 [Signal] |

Data out pointer.

din_i std_logic_vector ( 39 downto 0 ) [Signal] |

Data input.

dolo_en_i std_logic [Signal] |

Data output enable.

err_clr_i std_logic [Signal] |

Error clear.

error_i std_logic [Signal] |

Error.

h_abt_i std_logic [Signal] |

Hamming encoding.

h_err_i std_logic [Signal] |

Hamming encoding error.

hadd_o_i std_logic_vector ( 7 downto 0 ) [Signal] |

HW address.

i integer [Signal] |

Counter.

instr_err_i std_logic [Signal] |

Instruction error.

mixerror_i std_logic [Signal] |

Mixed error.

par_err_i std_logic [Signal] |

Parity error.

pop_i std_logic [Signal] |

Pop an event.

push_i std_logic [Signal] |

Push an event.

rd_bsl_i std_logic [Signal] |

Read baseline.

state_t ( idle , start , count1 , count2 , finish ) [Type] |

state type

trc_clr_i std_logic [Signal] |

Clear trigger.

trg_o_i std_logic [Signal] |

Trigger.

trg_overlap_i std_logic [Signal] |

Trigger overlap.

trsf_en_i std_logic [Signal] |

Enable transfer.

trsf_i std_logic [Signal] |

Transfer gate.

tstout_i std_logic [Signal] |

Test out.

TWX std_logic := ' 0 ' [Constant] |

wr_bsl_i std_logic [Signal] |

Write baseline.

write_i std_logic [Signal] |

write

The documentation for this class was generated from the following file:

- altro/altro.vhd

1.6.2-20100208

1.6.2-20100208