rcu_misc_pack Package Body Reference

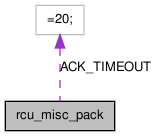

Collaboration diagram for rcu_misc_pack:

Functions | |

| std_logic_vector | int2slv ( val: in integer , width: in positive ) |

| string | slv2str ( input: in std_logic_vector ) |

| string | padstr ( constant what: in string ) |

| std_logic | parity ( constant x: in std_logic_vector ) |

Procedures | |

| wait_for_ack( signal rclk: in std_logic ,signal ackn: in std_logic ) | |

| wait_for_free( signal rclk: in std_logic ,signal ackn: in std_logic ) | |

| wait_for_trsf( signal rclk: in std_logic signal trsf: in std_logic signal bd: in out std_logic_vector ( 39 downto 0 ) ) | |

| spacer( signal rclk: in std_logic ) | |

| bus_raw_rw( constant data: in std_logic_vector ( 19 downto 0 ) constant addr: in std_logic_vector ( 39 downto 20 ) constant rw: in std_logic signal bd: out std_logic_vector ( 39 downto 0 ) signal writ: out std_logic signal cstb: out std_logic signal rclk: in std_logic signal ackn: in std_logic ) | |

| bus_rw( constant rw: in character constant bcast: in std_logic constant branch: in std_logic constant board: in std_logic_vector ( 3 downto 0 ) constant chip: in std_logic_vector ( 2 downto 0 ) constant channel: in std_logic_vector ( 3 downto 0 ) constant what: in bus_const_t constant data: in std_logic_vector ( 19 downto 0 ) signal bd: out std_logic_vector ( 39 downto 0 ) signal writ: out std_logic signal cstb: out std_logic signal clk: in std_logic signal ackn: in std_logic ) | |

| bus_send( constant name: in string ( 7 downto 1 ) constant rw: in character constant bcast: in std_logic constant branch: in std_logic constant board: in std_logic_vector ( 3 downto 0 ) constant chip: in std_logic_vector ( 2 downto 0 ) constant channel: in std_logic_vector ( 3 downto 0 ) constant data: in std_logic_vector ( 19 downto 0 ) signal bd: out std_logic_vector ( 39 downto 0 ) signal writ: out std_logic signal cstb: out std_logic signal clk: in std_logic signal ackn: in std_logic ) | |

| exec_command( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in bus_const_t constant bcast: in std_logic signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| exec_command( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in string constant bcast: in std_logic signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| exec_commands( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| read_register( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in bus_const_t signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| read_register( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in string signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| read_registers( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| write_register( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in bus_const_t constant data: in integer signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| write_register( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " constant what: in string constant data: in integer signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| write_registers( constant hadd: in std_logic_vector ( 4 downto 0 ) := " 00000 " signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

| make_trig( constant l0_delay: in time constant l1_delay: in time constant l2_delay: in time constant l0_len: in time constant l1_len: in time constant l2_len: in time signal l0: out std_logic signal l1: out std_logic signal l2: out std_logic signal name: out string ( 7 downto 1 ) ) | |

| make_trigger( signal l0: out std_logic signal l1: out std_logic signal l2: out std_logic signal name: out string ( 7 downto 1 ) ) | |

| rpinc( signal bd: in out std_logic_vector ( 39 downto 0 ) signal cstb: out std_logic signal writ: out std_logic signal ackn: in std_logic signal trsf: in std_logic signal rclk: in std_logic signal name: out string ( 7 downto 1 ) ) | |

Constants | |

| ACK_TIMEOUT | integer := 20 |

Member Function Documentation

| bus_raw_rw | (constant data in std_logic_vector(19 downto 0) , | |

| constant addr in std_logic_vector(39 downto 20) , | ||

| constant rw in std_logic , | ||

| signal bd out std_logic_vector(39 downto 0) , | ||

| signal writ out std_logic , | ||

| signal cstb out std_logic , | ||

| signal rclk in std_logic , | ||

| signal ackn in std_logic ) |

| bus_rw | (constant rw in character , | |

| constant bcast in std_logic , | ||

| constant branch in std_logic , | ||

| constant board in std_logic_vector(3 downto 0) , | ||

| constant chip in std_logic_vector(2 downto 0) , | ||

| constant channel in std_logic_vector(3 downto 0) , | ||

| constant what in bus_const_t , | ||

| constant data in std_logic_vector(19 downto 0) , | ||

| signal bd out std_logic_vector(39 downto 0) , | ||

| signal writ out std_logic , | ||

| signal cstb out std_logic , | ||

| signal clk in std_logic , | ||

| signal ackn in std_logic ) |

| bus_send | (constant name in string(7 downto 1) , | |

| constant rw in character , | ||

| constant bcast in std_logic , | ||

| constant branch in std_logic , | ||

| constant board in std_logic_vector(3 downto 0) , | ||

| constant chip in std_logic_vector(2 downto 0) , | ||

| constant channel in std_logic_vector(3 downto 0) , | ||

| constant data in std_logic_vector(19 downto 0) , | ||

| signal bd out std_logic_vector(39 downto 0) , | ||

| signal writ out std_logic , | ||

| signal cstb out std_logic , | ||

| signal clk in std_logic , | ||

| signal ackn in std_logic ) |

| exec_command | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in string , | ||

| constant bcast in std_logic , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| exec_command | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in bus_const_t , | ||

| constant bcast in std_logic , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| exec_commands | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| std_logic_vector int2slv | ( val in integer , | |

| width in positive ) |

| make_trig | (constant l0_delay in time , | |

| constant l1_delay in time , | ||

| constant l2_delay in time , | ||

| constant l0_len in time , | ||

| constant l1_len in time , | ||

| constant l2_len in time , | ||

| signal l0 out std_logic , | ||

| signal l1 out std_logic , | ||

| signal l2 out std_logic , | ||

| signal name out string(7 downto 1) ) |

| make_trigger | (signal l0 out std_logic , | |

| signal l1 out std_logic , | ||

| signal l2 out std_logic , | ||

| signal name out string(7 downto 1) ) |

| string padstr | (constant what in string ) |

| std_logic parity | (constant x in std_logic_vector ) |

| read_register | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in string , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| read_register | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in bus_const_t , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| read_registers | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| rpinc | (signal bd in out std_logic_vector(39 downto 0) , | |

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| string slv2str | ( input in std_logic_vector ) |

| spacer | (signal rclk in std_logic ) |

| wait_for_ack | (signal rclk in std_logic , | |

| signal ackn in std_logic ) |

| wait_for_free | (signal rclk in std_logic , | |

| signal ackn in std_logic ) |

| wait_for_trsf | (signal rclk in std_logic , | |

| signal trsf in std_logic , | ||

| signal bd in out std_logic_vector(39 downto 0) ) |

| write_register | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in string , | ||

| constant data in integer , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| write_register | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| constant what in bus_const_t , | ||

| constant data in integer , | ||

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

| write_registers | (constant hadd in std_logic_vector(4 downto 0):= "00000" , | |

| signal bd in out std_logic_vector(39 downto 0) , | ||

| signal cstb out std_logic , | ||

| signal writ out std_logic , | ||

| signal ackn in std_logic , | ||

| signal trsf in std_logic , | ||

| signal rclk in std_logic , | ||

| signal name out string(7 downto 1) ) |

Member Data Documentation

ACK_TIMEOUT integer := 20 [Constant] |

The documentation for this class was generated from the following file:

- rcu/rcu_misc.vhd

1.6.2-20100208

1.6.2-20100208