va1 Entity Reference

Inheritance diagram for va1:

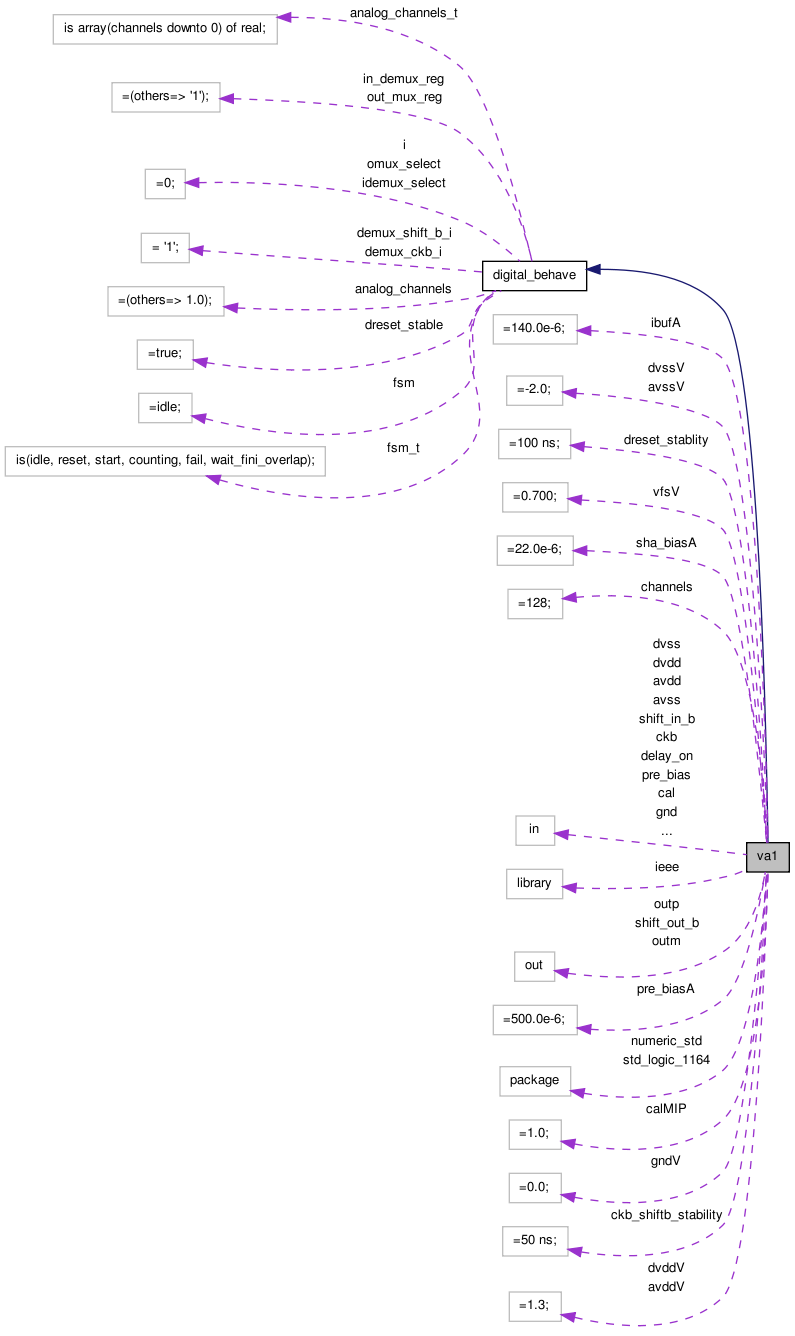

Collaboration diagram for va1:

Architectures | |

| digital_behave | Architecture |

Libraries | |

| ieee | |

Packages | |

| std_logic_1164 | |

| numeric_std | |

Generics | |

| channels | positive := 128 |

| gndV | real := 0.0 |

| dvddV | real := 1.3 |

| dvssV | real := -2.0 |

| avssV | real := -2.0 |

| pre_biasA | real := 500.0e-6 |

| sha_biasA | real := 22.0e-6 |

| ibufA | real := 140.0e-6 |

| vfsV | real := 0.700 |

| calMIP | real := 1.0 |

| avddV | real := 1.3 |

| dreset_stablity | time := 100 ns |

| ckb_shiftb_stability | time := 50 ns |

Ports | |

| gnd | in real := gndV |

| dvdd | in real := dvddV |

| dvss | in real := dvssV |

| delay_adjust | in real := gndV |

| delay_on | in real := dvssV |

| dummy_hold | in std_logic := ' 0 ' |

| dreset | in std_logic |

| dummy_dreset | in std_logic := ' 0 ' |

| shift_in_b | in std_logic := ' 1 ' |

| dummy_ck | in std_logic := ' 0 ' |

| ckb | in std_logic |

| shift_out_b | out std_logic := ' 1 ' |

| test_on | in std_logic := ' 0 ' |

| avss | in real := avssV |

| pre_bias | in real := pre_biasA |

| sha_bias | in real := sha_biasA |

| vref | in real |

| ibuf | in real := ibufA |

| outp | out real |

| outm | out real |

| vfs | in real := vfsV |

| cal | in real |

| avdd | in real := avddV |

| pad | in std_logic_vector ( channels -1 downto 0 ) |

Member Data Documentation

avddV real := 1.3 [Generic] |

avssV real := -2.0 [Generic] |

cal in real [Port] |

calMIP real := 1.0 [Generic] |

channels positive := 128 [Generic] |

ckb in std_logic [Port] |

ckb_shiftb_stability time := 50 ns [Generic] |

delay_adjust in real := gndV [Port] |

dreset in std_logic [Port] |

dreset_stablity time := 100 ns [Generic] |

dummy_ck in std_logic := ' 0 ' [Port] |

dummy_dreset in std_logic := ' 0 ' [Port] |

dummy_hold in std_logic := ' 0 ' [Port] |

dvddV real := 1.3 [Generic] |

dvssV real := -2.0 [Generic] |

gndV real := 0.0 [Generic] |

ibufA real := 140.0e-6 [Generic] |

ieee library [Library] |

numeric_std package [Package] |

outm out real [Port] |

outp out real [Port] |

pre_biasA real := 500.0e-6 [Generic] |

sha_biasA real := 22.0e-6 [Generic] |

shift_in_b in std_logic := ' 1 ' [Port] |

shift_out_b out std_logic := ' 1 ' [Port] |

std_logic_1164 package [Package] |

test_on in std_logic := ' 0 ' [Port] |

vfsV real := 0.700 [Generic] |

vref in real [Port] |

The documentation for this class was generated from the following file:

- va1/va1.vhd

1.6.2-20100208

1.6.2-20100208