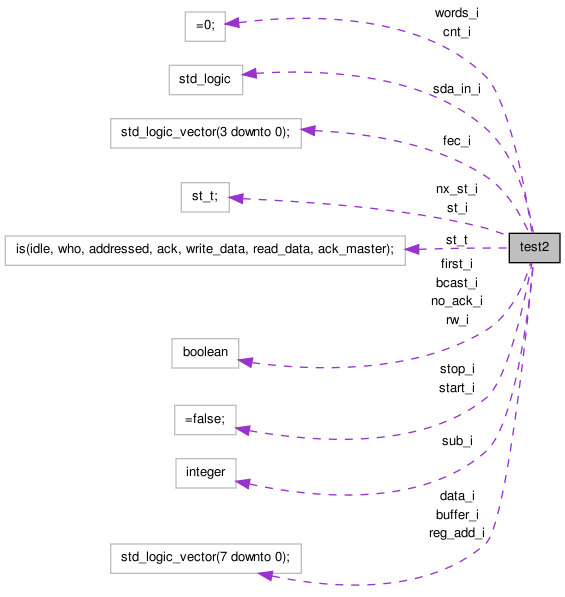

test2 Architecture Reference

List of all members.

Functions |

| | slv2str ( constant v: in ) |

| | Convert std_logic_vector to a string.

|

Processes |

| inputs | ( scl , start_i ) |

| nwords | ( scl , start_i ) |

| start_condition | ( sda_in , scl ) |

| stop_condition | ( sda_in , scl ) |

| count_scl | ( scl , start_i , stop_i ) |

| buffer_data | ( start_i , stop_i , scl ) |

| out_data | ( cnt_i ) |

| update_state | ( scl , stop_i ) |

| fsm | ( start_i , stop_i , st_i , cnt_i ) |

Procedures |

| | one_out(

signal sda_out: out

signal cnt: in

signal sub: in

signal data: in ( 15 downto 0 )

) |

Types |

| st_t | ( idle , who , addressed , ack , write_data , read_data , ack_master ) |

Signals |

| start_i | := false |

| stop_i | := false |

| cnt_i | := 0 |

| buffer_i | ( 7 downto 0 ) |

| rw_i | |

| sub_i | |

| no_ack_i | |

| words_i | := 0 |

| first_i | |

| sda_in_i | |

| fec_i | ( 3 downto 0 ) |

| bcast_i | |

| reg_add_i | ( 7 downto 0 ) |

| data_i | ( 7 downto 0 ) |

| st_i | st_t |

| nx_st_i | st_t |

Member Function Documentation

| buffer_data | |

( start_i , |

|

|

stop_i , |

|

|

scl ) |

[Process]

| count_scl | |

( scl , |

|

|

start_i , |

|

|

stop_i ) |

[Process]

| fsm | |

( start_i , |

|

|

stop_i , |

|

|

st_i , |

|

|

cnt_i ) |

[Process]

| inputs | |

( scl , |

|

|

start_i ) |

[Process]

| nwords | |

( scl , |

|

|

start_i ) |

[Process]

| one_out | |

(signal sda_out out std_logic , |

|

|

signal cnt in integer , |

|

|

signal sub in integer , |

|

|

signal data in std_logic_vector(15 downto 0) ) |

[Procedure]

| out_data | |

( cnt_i ) |

[Process]

| slv2str | |

(constant v in std_logic_vector ) |

[Function]

Convert std_logic_vector to a string.

- Parameters:

-

- Returns:

- String representation of v

| start_condition | |

( sda_in , |

|

|

scl ) |

[Process]

| stop_condition | |

( sda_in , |

|

|

scl ) |

[Process]

| update_state | |

( scl , |

|

|

stop_i ) |

[Process]

Member Data Documentation

data_i ( 7 downto 0 ) [Signal] |

fec_i ( 3 downto 0 ) [Signal] |

st_t ( idle , who , addressed , ack , write_data , read_data , ack_master ) [Type] |

The documentation for this class was generated from the following file:

1.6.2-20100208

1.6.2-20100208