MSM2_REGS Entity Reference

Inheritance diagram for MSM2_REGS:

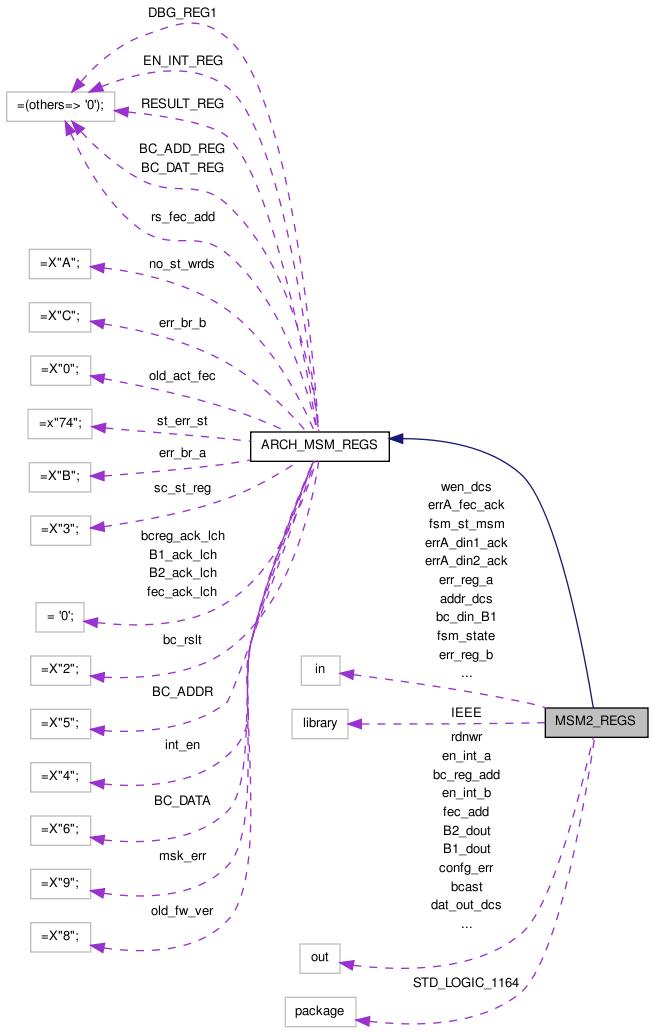

Collaboration diagram for MSM2_REGS:

Architectures | |

| ARCH_MSM_REGS | Architecture |

Libraries | |

| IEEE | |

Packages | |

| STD_LOGIC_1164 | |

Ports | |

| rst | in std_logic |

| clk | in std_logic |

| en_reg | in std_logic |

| wen_dcs | in std_logic |

| addr_dcs | in std_logic_vector ( 3 downto 0 ) |

| data_dcs | in std_logic_vector ( 31 downto 0 ) |

| dat_out_dcs | out std_logic_vector ( 31 downto 0 ) |

| rdnwr | out std_logic |

| Branch | out std_logic |

| bcast | out std_logic |

| fec_add | out std_logic_vector ( 3 downto 0 ) |

| bc_reg_add | out std_logic_vector ( 7 downto 0 ) |

| B1_dout | out std_logic_vector ( 7 downto 0 ) |

| B2_dout | out std_logic_vector ( 7 downto 0 ) |

| fec_act_list | in std_logic_vector ( 31 downto 0 ) |

| rcu_version | in std_logic_vector ( 31 downto 0 ) |

| err_reg_a | in std_logic_vector ( 31 downto 0 ) |

| err_reg_b | in std_logic_vector ( 31 downto 0 ) |

| sm_wrd_BA | in std_logic_vector ( 9 downto 0 ) |

| en_int_a | out std_logic |

| en_int_b | out std_logic |

| interruptA_in | in std_logic |

| interruptB_in | in std_logic |

| errA_fec_ack | in std_logic |

| errA_ack_bcR | in std_logic |

| errA_din1_ack | in std_logic |

| errA_din2_ack | in std_logic |

| errB_fec_ack | in std_logic |

| errB_ack_bcR | in std_logic |

| errB_din1_ack | in std_logic |

| errB_din2_ack | in std_logic |

| fsm_state | in std_logic_vector ( 15 downto 0 ) |

| fsm_st_msm | in std_logic_vector ( 4 downto 0 ) |

| confg_err | out std_logic_vector ( 7 downto 0 ) |

| clr_err | in std_logic |

| bc_din_B1 | in std_logic_vector ( 7 downto 0 ) |

| bc_din_B2 | in std_logic_vector ( 7 downto 0 ) |

Member Data Documentation

addr_dcs in std_logic_vector ( 3 downto 0 ) [Port] |

B1_dout out std_logic_vector ( 7 downto 0 ) [Port] |

B2_dout out std_logic_vector ( 7 downto 0 ) [Port] |

bc_din_B1 in std_logic_vector ( 7 downto 0 ) [Port] |

bc_din_B2 in std_logic_vector ( 7 downto 0 ) [Port] |

bc_reg_add out std_logic_vector ( 7 downto 0 ) [Port] |

bcast out std_logic [Port] |

Branch out std_logic [Port] |

clk in std_logic [Port] |

clr_err in std_logic [Port] |

confg_err out std_logic_vector ( 7 downto 0 ) [Port] |

dat_out_dcs out std_logic_vector ( 31 downto 0 ) [Port] |

data_dcs in std_logic_vector ( 31 downto 0 ) [Port] |

en_int_a out std_logic [Port] |

en_int_b out std_logic [Port] |

en_reg in std_logic [Port] |

err_reg_a in std_logic_vector ( 31 downto 0 ) [Port] |

err_reg_b in std_logic_vector ( 31 downto 0 ) [Port] |

errA_ack_bcR in std_logic [Port] |

errA_din1_ack in std_logic [Port] |

errA_din2_ack in std_logic [Port] |

errA_fec_ack in std_logic [Port] |

errB_ack_bcR in std_logic [Port] |

errB_din1_ack in std_logic [Port] |

errB_din2_ack in std_logic [Port] |

errB_fec_ack in std_logic [Port] |

fec_act_list in std_logic_vector ( 31 downto 0 ) [Port] |

fec_add out std_logic_vector ( 3 downto 0 ) [Port] |

fsm_st_msm in std_logic_vector ( 4 downto 0 ) [Port] |

fsm_state in std_logic_vector ( 15 downto 0 ) [Port] |

IEEE library [Library] |

interruptA_in in std_logic [Port] |

interruptB_in in std_logic [Port] |

rcu_version in std_logic_vector ( 31 downto 0 ) [Port] |

rdnwr out std_logic [Port] |

rst in std_logic [Port] |

sm_wrd_BA in std_logic_vector ( 9 downto 0 ) [Port] |

STD_LOGIC_1164 package [Package] |

wen_dcs in std_logic [Port] |

The documentation for this class was generated from the following file:

- msmodule2/msm2_decoder/msm2_regs/msm2_regs.vhd

1.6.2-20100208

1.6.2-20100208